Intro to Arduino Assembly – Class Lectures

Introduction to AVR Assembly Language Programming

READING

The AVR Microcontroller and Embedded Systems using Assembly and C by Muhammad Ali Mazidi, Sarmad Naimi, and Sepehr Naimi

Sections: 0.1, 0.2, 1.1, 2.5, 2.6, 2.7

SOURCE MATERIAL

These are some of the sources I used to develop the material used in the lecture series.

- Reduced Instruction Set Computer

- Atmel AVR Assembler User Guide

- Atmel AVR

- AVR Quick Reference Guide:

- ATmega328P Summary (26 pages)

- ATmega328P (448 pages)

- 8-bit AVR Instruction Set (155 pages)

Table of Contents

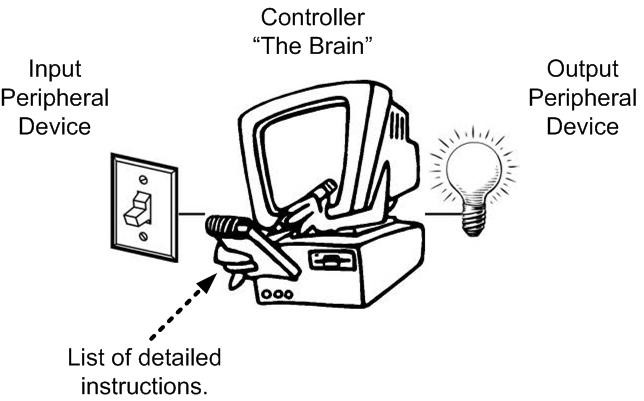

What is an Embedded System?

- An embedded system is an electronic system that contains at least one controlling device, i.e. “the brain”, but in such a way that it is hidden from the end user. That is, the controller is embedded so far in the system that usually users don’t realize its presence.

- Embedded systems perform a dedicated function.

What is the Controlling Device?

| EE Course | Technology | Tools |

| EE201 | Discrete Logic | Boolean Algebra |

| EE301 | Field Programmable Gate Array (FPGA), Application-Specific Integrated Circuit (ASIC) | HDL (typically VHDL or Verilog) |

| EE346 | Microcontroller | Program (typically C++ or Assembly) |

| EE443 | System on a Chip (SoC) | System Level Design Language |

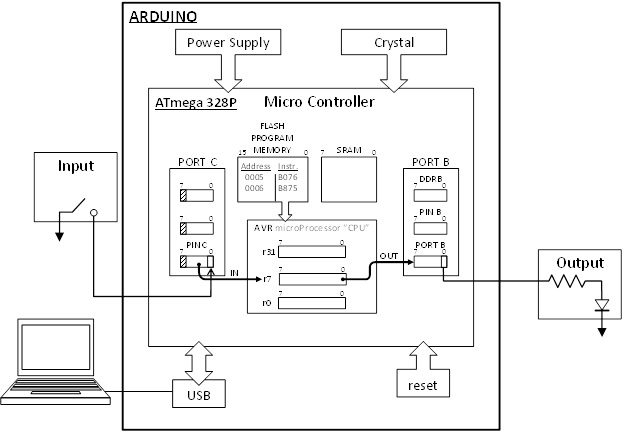

What is an Arduino?

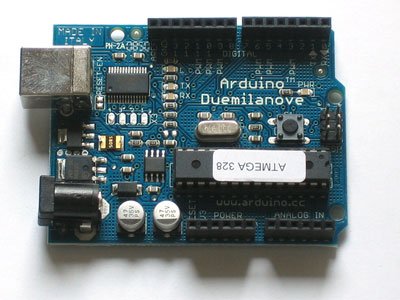

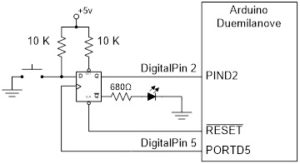

- Arduino is an open-source electronics PCB containing a microcontroller and the things needed to support it: Power Supply, Communications, Reset Button, Clock, and Connectors for adding Sensors and Actuators in the physical world.

-

Using an Arduino you can develop interactive objects, taking inputs from a variety of switches or sensors, and controlling a variety of lights, motors, and other physical outputs.

- The Arduino consists of two parts; the hardware and the software.

- We will be using the Arduino Uno which contains an ATmega328P 8 bit microcontroller.

- We will be using AVR Studio to develop the software for the Arduino in place of the Arduino IDE and associated Scripting Language.

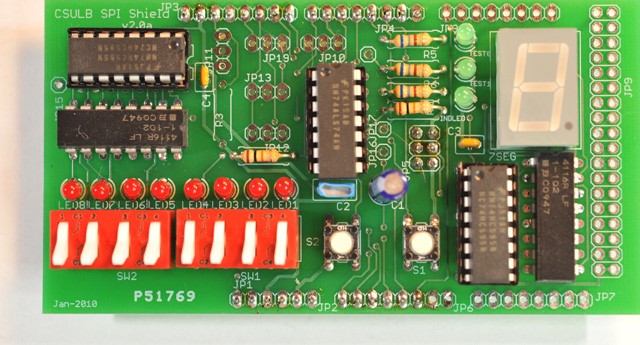

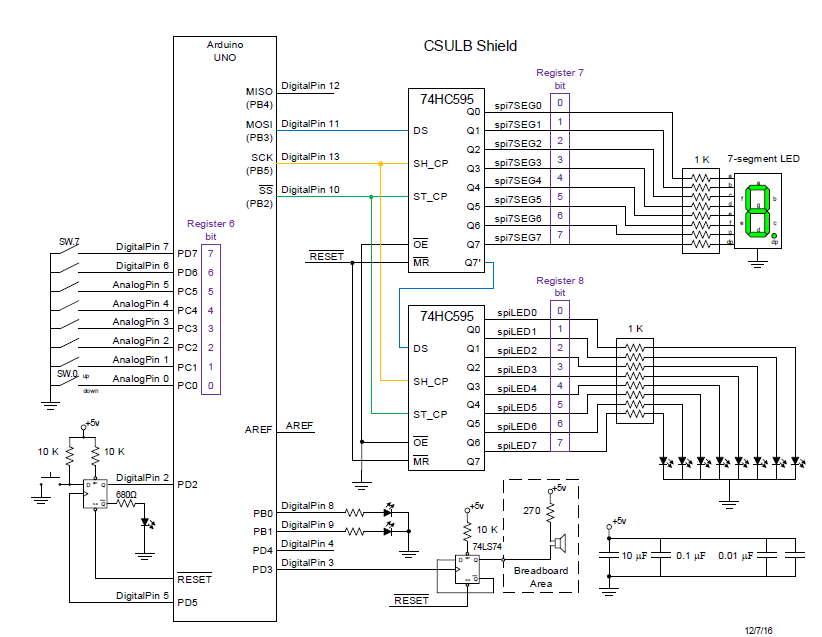

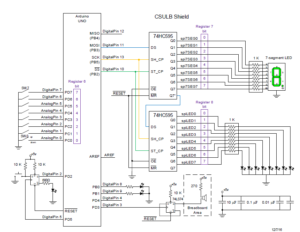

What is a CSULB Shield?

The CSULB Shield was designed to meet the educational objectives of EE 346.

The shield works with the Arduino Uno, Duemilanove (rev 2009b), and Mega Microcontroller Boards.

CSULB Shield Specifications

- Input

- 8 Toggle Switches

- General Purpose Push Button

- Reset Button

- Output

- 8 Discrete Red LEDs

- 3 Discrete Green LEDs

- 1 7-Segment Display

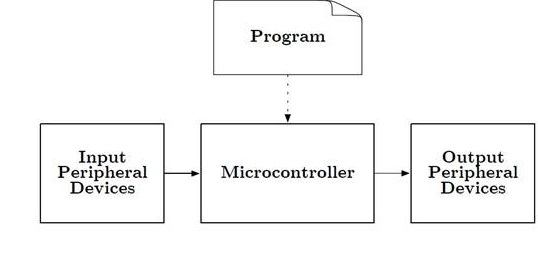

Building Blocks

What is an Input and Output Peripheral Device?

- A device attached to a controlling mechanism, for example a computer, yet is not actually part of the controlling mechanism, and whose operation is functionally dependent upon the controlling mechanism.

How do you design this controlling mechanism?

- If you control peripherals using Discrete Electronics or a Programmable Logic Device (PLD) such as an FPGA or ASIC, then the control is in hardware (EE201, EE301).

- If you control peripherals using a Microcontroller then the control is in software (EE346 and EE444), implemented by a Program.

- If you control peripheral using a System on a Chip (SoC) then the control may be in software and/or hardware (EE443).

What is a Program?

- The Program is a “very specific list of instructions” to the computer.

- The process of “creating the program” is where much of an electrical engineer’s time is spent.

- The program is often referred to as Software, while the physical system components are called Hardware. Software held within non-volatile memory is called Firmware.

- Software design is all about creating patterns of 0’s and 1’s in order to get the computer to do what we want. These 0’s and 1’s are known as Machine Code.

0010 0111 0000 0000 → 1110 1111 0001 1111 → 1011 1001 0000 0111 → 1011 1001 0001 1000

1011 1001 0000 0100 → 1011 0000 0111 0110 → 1011 1000 0111 0101 → 1100 1111 1111 1101

- The architecture of the processer (or computer) within a microcontroller is unique as are the Machine Code Instructions it understands.

0010 0111 0000 0000

1110 1111 0001 1111

- The list of Machine Code Instructions understood by a Microcontroller is known as the Machine Language.

How is Machine Code Related to Assembly Language?

Machine Code (The language of the machine)

- Binary Code (bit sequence) that directs the computer to carry out (execute) a pre-defined operation.

0010 0111 0000 0000

1110 1111 0001 1111

1011 1001 0000 0111

1011 1001 0001 1000

Assembly Language

- A computer language where there is a one-to-one correspondence between a symbolic (assembly language instruction) and a machine code

- The language of the machine in human readable form

clr r16

ser r17

out DDRC, r16

out PORTC, r17

Corollary

- Specific to a single computer or class of computers (non-portable)

Anatomy of an Assembly Instruction?

Sample Code Segment

| Machine Code | Assembly Code | |

| Binary | Hex | |

| 0010 0111 0000 0000 | 0x2700 | clr r16 |

| 1110 1111 0001 1111 | 0xEF1F | ser r17 |

| 1011 1001 0000 0111 | 0xB907 | out DDRC, r16 |

| 1011 1001 0001 1000 | 0xB918 | out PORTC, r17 |

- The Operation Code or Opcode for short, is a mnemonic that tells the CPU what instruction is to be executed. In the sample code above that would be clr (clear), ser (set register), and out (output to I/O location). One or more operands follow the Opcode.

- The Operand(s) specify the location of the data that is to be operated on by the CPU. In many cases it is the Arithmetic Logic Unit (ALU) that performs the specified operation.

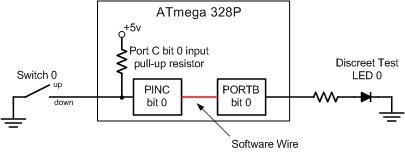

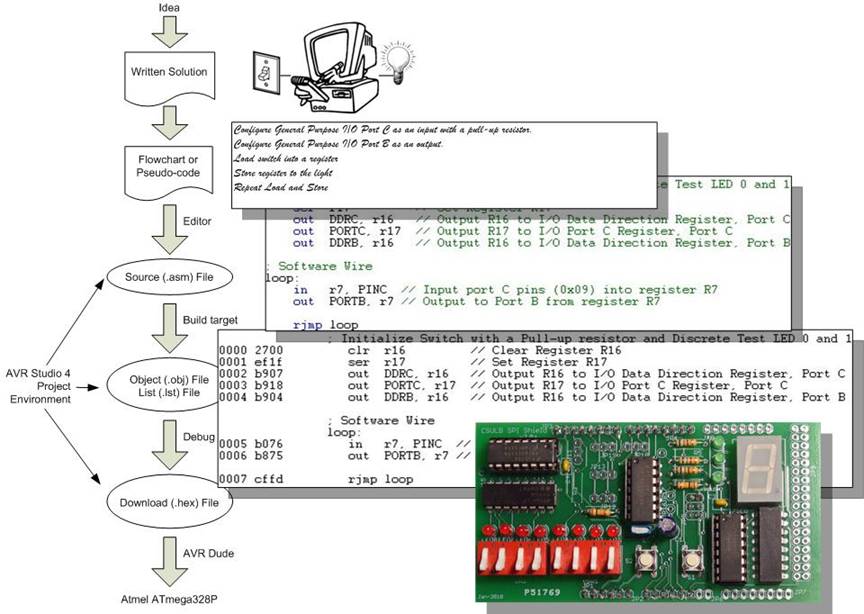

Design Example

Write an Assembly Program to turn a light on and off with a switch. A similar program was used in the design of The Wake-up Machine.

Development Steps

Assembly and Microcontroller Overview

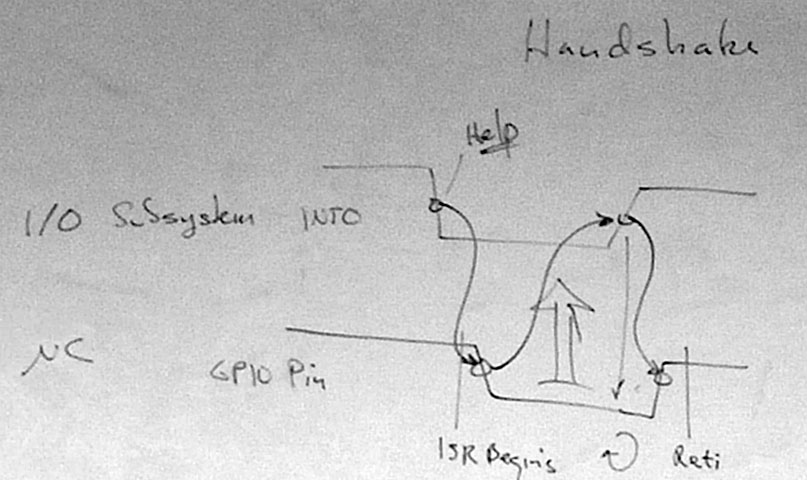

Help

0010 0111 0000 00002 = 270016 = clr r16

An Important part of this course is understanding the Design and Language of “The Computer.”

The computer implements the classical digital gate you learned in your Digital Logic class (EE201) in software with instructions like and, or, and eor/xor.

You are also going to have to seamlessly move from binary to hexadecimal and back again (i.e., Number Systems).

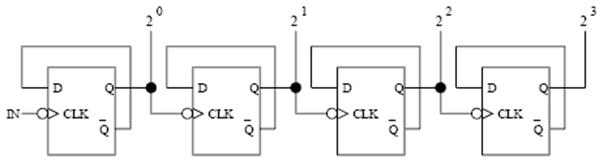

Computer programs move data through Registers, so a working knowledge of Flip-Flops and Registers is also an important foundational part of this class.

Finally, instead of designing with gates (EE201) you will be designing with code. So you will need to review Programming concepts like: data transfer (assignment expressions) , arithmetic and logic operators, control transfer (branching and looping), and bit and bit test operators that you leaned in your programming class (CECS174 or CECS100).

The good news is that help is available in Chapter 0: “Introduction to Computing” of your textbook, the supplemental reading provided at the beginning of this document, the web, and the following sections.

Numbers and Their Computer Representation Number System.

Introduction

Base 10 result of ten fingers

Arabic symbols 0-9, India created Zero and Positional Notation

Other Systems: Roman Numerals: essentially additive, Importance of Roman Numeral lies in whether a symbol precedes or follows another symbol. Ex. IV = 4 versus VI = 6. This was a very clumsy system for arithmetic operations.

Positional Notation (Positive Real Integers)

Fractional numbers will not be considered but it should be noted that the addition of said would be a simple and logical addition to the theory presented.

The value of each digit is determined by its position. Note pronunciation of 256 “Two Hundred and Fifty Six?

Ex. 256 = 2*102 + 5*101 + 6*100

Generalization to any base or radix

Base or Radix = Number of different digit which can occur in each position in the number system.

N = Anrn + An-1rn-1 + … + A1r1 + A0r0 (or simple A1r + A0)

Binary

The operation of most digital devices is binary by nature, either they are on or off.

Examples: Switch, Relay, Tube, Transistor, and Transistor-Transisor-Logic Integrated circuit (TTL IC)

Thus it is only logical for a digital computer to in base 2.

Note: Future devices may not have this characteristic, and this is one of the reasons the basics and theory are important. For they add flexibility to the system.

In the Binary system there are only 2 states allowed; 0 and 1 (FALSE or TRUE, OFF or ON)

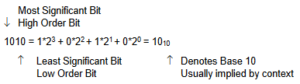

Example: Most Significant Bit

Bit = One Binary Digit (0 or 1)

Bit = One Binary Digit (0 or 1)

This positional related equation also gives us a tool for converting from a given radix to base 10 – in this example Binary to Decimal.

Base Eight and Base Sixteen

Early in the development of the digital computer Von Neuman realized the usefulness of operating in intermediate base systems such as base 8 (or Octal)

By grouping 3 binary digits or bits one octal digit is formed. Note that 23 = 8

Binary to Octal Conversion Table

222120

0 0 0 = 0

0 0 1 = 1

0 1 0 = 2

0 1 1 = 3

1 0 0 = 4

1 0 1 = 5

1 1 0 = 6

1 1 1 = 7

Symbols (not numbers) 8 and 9 are not used in octal.

Example: 100 001 010 110

4 1 2 6 8 = 4*83 + 1*82 + 2*81 + 6*80 = 2134

This is another effective way of going from base 2 to base 10

Summary: Base 8 allows you to work in the language of the computer without dealing with large numbers of ones and zeros. This is made possible through the simplicity of conversion from base 8 to base 2 and back again.

In microcomputers groupings of 4 bits (as opposed to 3 bits) or base 16 (24) is used. Originally pronounced Sexadecimal, base 16 was quickly renamed Hexadecimal (this really should be base 6).

Binary to Hex Conversion Table

0 0 0 0 = 0

0 0 0 1 = 1

0 0 1 0 = 2

0 0 1 1 = 3

0 1 0 0 = 4

0 1 0 1 = 5

0 1 1 0 = 6

0 1 1 1 = 7

1 0 0 0 = 8

1 0 0 1 = 9

1 0 1 0 = A

1 0 1 1 = B

1 1 0 0 = C

1 1 0 1 = D

1 1 1 0 = E

1 1 1 1 = F

In Hex Symbols for 10 to 15 are borrowed from the alphabet. This shows how relative numbers really are or in other words, they truly are just symbols.

Example: 1000 0101 0110

8 5 6 16 = 8*162 + 5*161 + 6*160 = 2134

It is not as hard to work in base 16 as you might think, although it does take a little practice.

Conversion from Base 10 to a Given Radix (or Base)

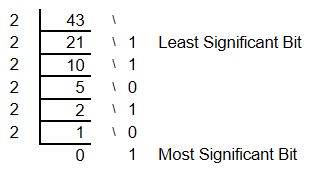

Successive Division is best demonstrated by an example

To get the digits in the right order let them fall to the right.

For this example: 4310 = 1010112 Quick Check (Octal) 101 011 = 5*8 + 3 = 4310

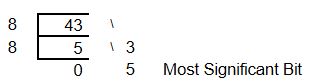

Another example: Convert 4310 from decimal to Octal

For this example: 4310 = 538 Quick Check (Octal) 5*8 + 3 = 4310

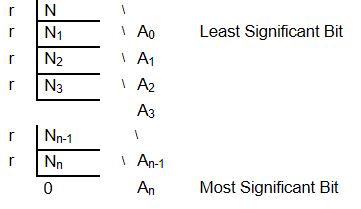

Generalization of the procedure OR Why It Works

Where r = radix, N = number, A = remainder, and n = the number of digits in radix r for number N. Division is normally done in base 10.

Another way of expressing the above table is:

N = r*N1 + A0

N1 = r*N2 + A1

N2 = r*N3 + A2

:

Nn-1 = r*Nn + An-1

Nn = r*0 + An

or (now for the slight of hand)

N = r*( r*N2 + A1)+ A0 substitute N1

N = r2N2 + rA1+ A0 multiply r through equation

N = r2(r*N3 + A2) + rA1+ A0 substitute N2

:

N = Anrn + An-1rn-1 + … + A1r1 + A0r0

Nomenclature

Bit = 1 binary digit

Byte = 8 bits

Nibble = one half byte = 4 bits

Word = Computer Dependent

Arithmetic Operations

Addition

Binary

Binary addition is performed similar to decimal addition using the following binary addition rules:

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10 (0 with a carry of 1)

Examples:

| Problem | 2110 + 1010 = 3110 | 4510 + 5410 = 9910 | 310 + 710 = 1010 |

| 101012

+ 010102 _______________ 111112 |

1011012

+ 1101102 _______________ 11000112 |

0112

+ 1112 _______________ 10102 |

|

| Check | 1*23 + 0*22 + 1*21 + 0*20 =

1*8 + 0*4 + 1*2 + 0*1 = 1010 |

Octal

Octal addition is also performed similar to decimal addition except that each digit has a range of 0 to 7 instead of 0 to 9.

| Problem | 2110 + 1010 = 3110 | 4510 + 5410 = 9910 | 310 + 710 = 1010 |

| 258

+ 128 _______________ 378 |

558 + 668 _______________ 1438 |

38 + 78 _______________ 128 |

|

| Check | 3*81 + 7*80

3*8 + 7*1 = 3110 |

1*82 + 4*81 + 3*80

64 + 32 + 3 = 9910 |

1*81 + 2*80

8 + 2 = 1010 |

Hexadecimal

Hex addition is also performed similar to decimal addition except that each digit has a range of 0 to 15 instead of 0 to 9.

| Problem | 2110 + 1010 = 3110 | 4510 + 5410 = 9910 | 310 + 710 = 1010 |

|

1516 + 0A16 _______________ 1F16 |

2D16 + 3616 _______________ 6316 |

316 + 716 _______________ A16 (not 10) |

|

| Check | 1*161 + 15*160

16 + 15 = 3110 |

6*161 + 3*160

96 + 3 = 9910 |

10*160

1010 |

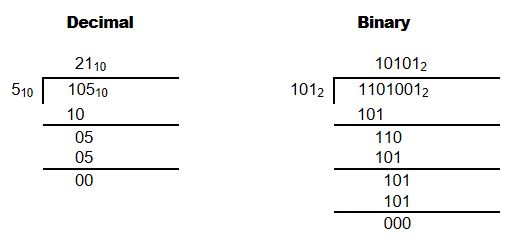

Binary Multiplication

| Decimal | Binary |

|

1110 x 1310 _______________ 3310 1110– _______________ 14310 |

10112 x 11012 _______________ 10112 00002- 10112– 10112— _______________ 100011112 |

| Check | 8*161 + 15*160

128 + 15 = 14310 |

Binary Division

Check: 1*161 + 5*160 = 16 + 5 = 2110

Practice arithmetic operations by making problems up and then checking your answers by converting them back to base 10 via different bases (i.e., 2, 8, and 16).

How a computer performs arithmetic operations is a much more involved subject and has not been dealt with within this section.

Complements and Negative Numbers OR Adding a Sign Bit

Addition, Multiplication, and Division is nice but what about subtraction and negative numbers? From grade school you have learned that subtraction is simply the addition of a negative number. Mathematicians along with engineers have exploited this principle along with modulo arithmetic — a natural outgrowth of adders of finite width — to allow computers to operate on negative numbers without adding any new hardware elements to the arithmetic logic unit (ALU).

Sign Magnitude

Here is a simple solution, just add a sign bit. To implement this solution in hardware you will need to create a subtractor; which means more money.

sign magnitude

Example: – 2 = 1 00102

Ones Complement

Here is a solution that is a little more complex. Add the sign bit and invert each bit making up the magnitude — simply change the 1’s to 0’s and the 0’s to 1’s.

sign magnitude

Example: – 2 = 1 11012

To subtract in 1’s complement you simply add the sign and magnitude bits letting the last carry bit (from the sign) fall into the bit bucket, and then add 1 to the answer. Once again let the last carry bit fall into the bit bucket. The bit bucket is possible due to the physical size of the adder.

0 10102 10

+ _ 1 11012 +(-2)

0 10002 8

+______12 Adjustment

0 10012

Although you can now use your hardware adder to subtract numbers, you now need to add 1 to the answer. This again means adding hardware. Compounding this problem, ones complement allows two numbers to equal 0 (schizophrenic zero).

Twos Complement

Here is a solution that is a little more complex to set up, but needs no adjustments at the end of the addition. There are two ways to take the twos complement of a number.

Method 1 = Take the 1’s complement and add 1

__0 00102 2 <- start

+ 1 11012 1’s complement (i.e. invert)

+ 12 add 1

1 11102

Method 2 = Move from right to left until a 1 is encountered then invert.

| 0 00102 | start = 210 |

| 02 | no change |

| 102 | no change but one is encountered |

| 1102 | invert = change 0 to 1 |

| 11102 | invert = change 0 to 1 |

| 1 11102 | invert = change 0 to 1 |

Subtraction in twos complement is the same as addition. No adjustment is needed, and twos complement has no schizophrenic zero although it does have an additional negative number (see How It Works).

0 10102 10

+ 1 11102 +(-2)

0 10012 8

Examples:

| Problem | 3310 – 1910 = 1410 | 6910 – 8410 = -1510 |

|

0 1000012 + 1 1011012 _______________ 0 0011102 |

0 10001012 + 1 01011002 _______________ 1 11100012 |

|

| Check | convert to intermediate base E16 = 1410 | convert back to sign magnitude

– 00011112 convert to intermediate base (16) – F16 = – 1510 |

Why It Works

Real adders have a finite number of bits, which leads naturally to modulo arithmetic — the bit bucket.

With arithmetic now reduced to going around in circles, positive numbers can add up to negative and vice-versa. Two tests provide a quick check on whether or not an “Overflow” condition exists.

Test 1 = If the two numbers are negative and the answer is positive, an overflow has occurred.

Test 2 = If the two number are positive and the answer is negative, an overflow has occurred.

If computers were calculators and the world was a perfect place, we would be done. But they are not and so we continue by looking at a few real world problems and their solutions.

Character Codes OR Non-Numeric Information

Decimal Number Problems

Represent a Decimal Numbers in a Binary Computer. A binary representation of a decimal number, a few years ago, might have been “hard wired” into the arithmetic logic unit (ALU) of the computer. Today it, more likely than not, is simply representing some information that is naturally represented in base 10, for example your student ID.

Solution

In this problem, ten different digits need to be represented. Using 4 bits 24 or 16 combinations can be created. Using 3 bits 23 or 8 combinations can be created. Thus 4 bits will be required to represent one Decimal Digit. It should here be pointed out how 16 combinations can be created from 4 bits (0000 – 1111) while the largest numeric value that can be represented is 15. The reason that the highest numeric value and the number of combinations are different, is due to zero (0) being one of the combinations. This difference points up the need to always keep track of wetter or not you are working zero or one relative and what exactly you are after — a binary number or combinations.

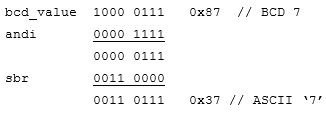

The most common way of representing a decimal number is named Binary Coded Decimal (BCD). Here each binary number corresponds to its decimal equivalent, with numbers larger than 9 simply not allowed. BCD is also known as an 8-4-2-1 code since each number represents the respective weights of the binary digits. In contrast the Excess-3 code is an unweighted code used in earlier computers. Its code assignment comes from the corresponding BCD code plus 3. The Excess-3 code had the advantage that by complementing each digit of the binary code representation of a decimal digit (1’s complement), the 9’s complement of that digit would be formed. The following table lists each decimal digit and its BCD and Excess-3 code equivalent representation. I have also included the negative equivalent of each decimal digit encoded using the Excess-3 code. For instance, the complement of 0100 (1 decimal) is 1011, which is 8 decimal. You can find more decimal codes on page 18 of “Digital Design” by M. Morris Mano (course text).

| Binary Coded Decimal (BCD) | Excess-3 | |||

| Decimal Digit | Binary Code 8‑4-2-1 | Decimal Digit | Binary Code | 9’s Compliment |

|

0 1 2 3 4 5 6 7 8 9 N/A N/A N/A N/A N/A N/A |

0000

0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 |

N/A

N/A N/A 0 1 2 3 4 5 6 7 8 9 N/A N/A N/A |

0000

0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 |

1111 1110 1101 1100 1011 1010 1001 1000 0111 0110 0101 0100 0011 0010 0001 0000 |

Alphanumeric Character Problem

Represent Alphanumeric data (lower and upper case letters of the alphabet (a-z, A-Z), digital numbers (0-9), and special symbols (carriage return, line feed, period, etc.).

Solution

To represent the upper and lower case letters of the alphabet, plus ten numbers, you need at least 62 (2×26+10) unique combinations. Although a code using only six binary digits providing 26 or 64 unique combinations would work, only 2 combinations would be left for special symbols. On the other hand a code using 7 bits provides 27 or 128 combinations, which provides more than enough room for the alphabet, numbers, and special symbols. So who decides which binary combinations correspond to what character. Here there is no “best way.” About thirty years ago IBM came out with a new series of computers which used 8 bits to store one character (28 = 256 combinations), and devised the Extended Binary-Coded Decimal Interchange Code (EBCDIC pronounced ep-su-dec) for this purpose. Since IBM had a near monopoly on the computer field, at that time, the other computer makers refused to adopt EBCDIC, and that is how the 7bit American Standard Code for Information Interchange (ASCII) came into existence. ASCII has now been adopted by virtually all micro-computer and mini-computer manufacturers. The table below shows a partial list of the ASCII code. Page 23 of the text lists all 128 codes with explanations of the control characters.

| DEC | HEX | CHAR | DEC | HEX | CHAR |

| 32

33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 |

20

21 22 23 24 25 26 27 28 29 2A 2B 2C 2D 2E 2F 30 31 32 33 34 35 36 37 38 39 3A 3B 3C 3D 3E 3F |

!

“ # $ % & ‘ ( ) * + , – * / 0 1 2 3 4 5 6 7 8 9 : ; < = > ? |

64

65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 |

40

41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57 58 59 5A 5B 5C 5D 5E 5F |

@

A B C D E F G H I J K L M N O P Q R S T U V W X Y Z [ \ ] ^ _ |

The word “string” is commonly used to describe a sequence of characters stored via their numeric codes — like ASCII).

Although ASCII requires only 7 bits, the standard in computers is to use 8 bits, where the leftmost bit is set to 0. This allows you to code another 128 characters (including such things as Greek letters), giving you an extended character set, simply by letting the leftmost bit be a 1. This can also lead to a computer version of the tower of Babel. Alternatively, the leftmost bit can be used for detecting errors when transmitting characters over a telephone line. Which brings us to our next problem.

Synthesis

Although ASCII solves the communication problem between English speaking computers, what about Japanese, Chinese, or Russian computers which have different, and in all these examples, larger alphabets?

Communication Problem

Binary information may be transmitted serially (one bit at a time) through some form of communication medium such as a telephone line or a radio wave. Any external noise introduced into the medium can change bit values from 1 to 0 or visa versa.

Solution

The simplest and most common solution to the communication problem involves adding a parity bit to the information being sent. The function of the parity bit is to make the total number of 1’s being sent either odd (odd parity) or even (even parity). Thus, if any odd number of 1’s were sent but an even number of 1’s received, you know an error has occurred. The table below illustrates the appropriate parity bit (odd and even) that would be appended to a 4-bit chunk of data.

Synthesis

What happens if two binary digits change bit values? Can a system be devised to not only detect errors but to identify and correct the bit(s) that have changed? One of the most common error-correcting codes was developed by R.W. Hamming. His solution, known as a Hamming code, can be found in a very diverse set of places from a Random Access Memory (RAM) circuit to a Spacecraft telecommunications link. For more of error correcting codes read pages 299 to 302 of the text.

Although detecting errors is nice, preventing them from occurring is even better. Which of course brings us to our next problem.

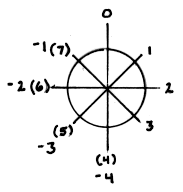

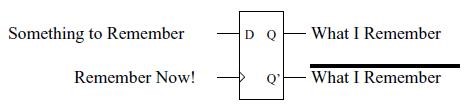

Shaft Encoder Problem

As a shaft turns, you need to convert its radial position into a binary coded digital number.

Solution

The type of coder which will be briefly described below converts a shaft position to a binary-coded digital number. A number of different types of devices will perform this conversion; the type described is representative of the devices now in use, and it should be realized that more complicated coders may yield additional accuracy. Also, it is generally possible to convert a physical position into an electric analog-type signal and then convert this signal to a digital system. In general, though, more direct and accurate coders can be constructed by eliminating the intermediate step of converting a physical position to an analog electric signal. The Figure below illustrates a coded-segment disk which is coupled to the shaft.

The shaft encoder can be physically realized using electro-mechanical (brush) or electro-optical technology. Assuming an electro-optical solution, the coder disk is constructed with bands divided into transparent segments (the shaded areas) and opaque segments (the unshaded areas). A light source is put on one side of the disk, and a set of four photoelectric cells on the other side, arranged so that one cell is behind each band of the coder disk. If a transparent segment is between the light source and a light-sensitive cell, a 1 output will result; and if an opaque area is in front of the photoelectric cell, there will be a O output.

There is one basic difficulty with the coder illustrated: if the disk is in a position where the output number is changing from 011 to 100, or in any position where several bits are changing value, the output signal may become ambiguous. As with any physically realized device, no matter how carefully it is made, the coder will have erroneous outputs in several positions. If this occurs when 011 is changing to 100, several errors are possible; the value may be read as 111 or 000, either of which is a value with considerable errors. To circumvent this difficulty, engineers use a “Gray,” or “unit distance,” code to form the coder disk (see previous Figure). In this code, 2 bits never change value in successive coded binary numbers. Using a Gray coded disk, a 6 may be read as 7, or a 4 as 5, but larger errors will not be made. The Table below shows a listing of a 4-bit Gray code.

| Decimal | Gray Code |

|

0 |

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000 |

Synthesis

Gray code is used in a multitude of applications other than shaft encoders. For example, CMOS circuits draw the most current when they are switching. If a large number of circuits switch at the same time unwelcome phenomena such as “Ground Bounce” and “EMI Noise” can result. If the transistors are switching due to some sequential phenomena (like counting), then these unwelcome visitors can be minimized by replacing a weighted binary code by a Gray code.

If the inputs to a binary machine are from an encoder using a Gray code, each word must be converted to a conventional binary or binary-coded decimal bit equivalent. How can this be done? Before you can answer this question, you will need to learn about Boolean Algebra — what a coincidence, that’s the topic of the next section.

Introduction to the Atmel AVR Family of Microcontrollers

READING

The AVR Microcontroller and Embedded Systems using Assembly and C

by Muhammad Ali Mazidi, Sarmad Naimi, and Sepehr Naimi

Sections: 0.3, 0.4, 1.2, 2.1, 2.2, 2.8, 2.9, 3.3

SOURCE MATERIAL

- Reduced Instruction Set Computer: http://en.wikipedia.org/wiki/Load-store_architecture

- Atmel AVR: http://en.wikipedia.org/wiki/Atmel_AVR

- AVR Quick Reference Guide: http://www.atmel.com/dyn/resources/prod_documents/doc4064.pdf

- ATmega328P Summary (26 pages) http://www.atmel.com/dyn/resources/prod_documents/8161S.pdf

- Arduino Uno schematic

- Arduino shield

- ATmega328P (448 pages) http://www.atmel.com/dyn/resources/prod_documents/doc8161.pdf

- 8-bit AVR Instruction Set (155 pages) http://www.atmel.com/dyn/resources/prod_documents/doc0856.pdf

Table of Contents

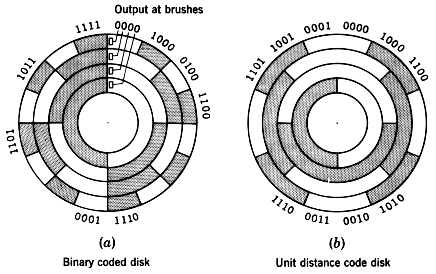

WHAT IS A FLIP-FLOP AND A REGISTER

You can think of a D flip-flop as a one-bit memory. As illustrated, the something to remember on the D input of flip-flop is remembered on the positive edge of the clock input.

Truth Table

| Dt | Qt+1 | |

| 0 | 0 | |

| 1 | 1 | |

| x | Qt |

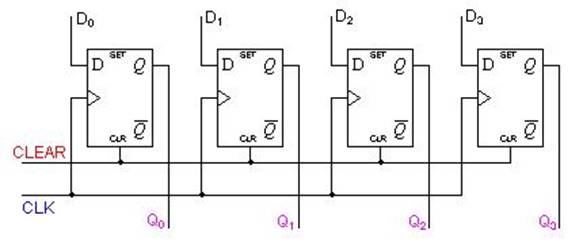

A register is a collection of flip-flops sharing the same clock input.

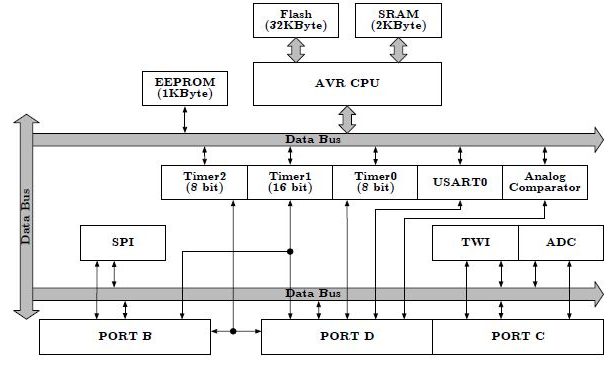

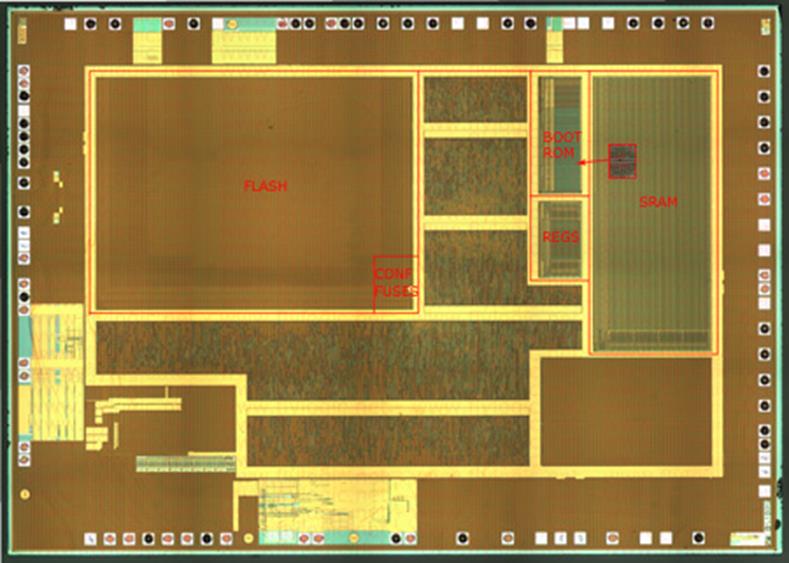

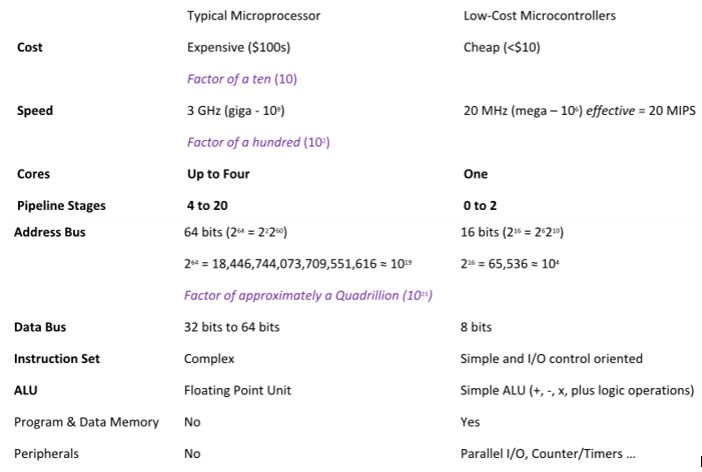

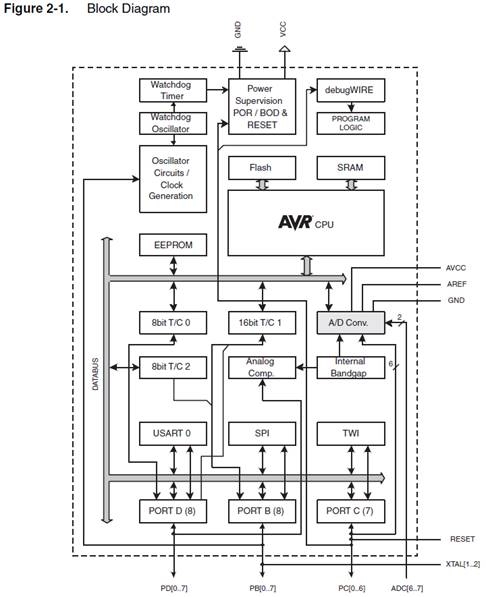

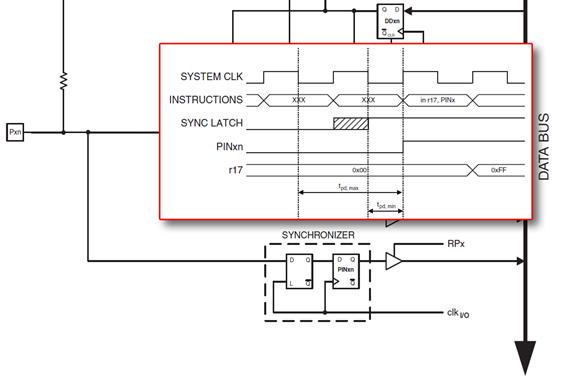

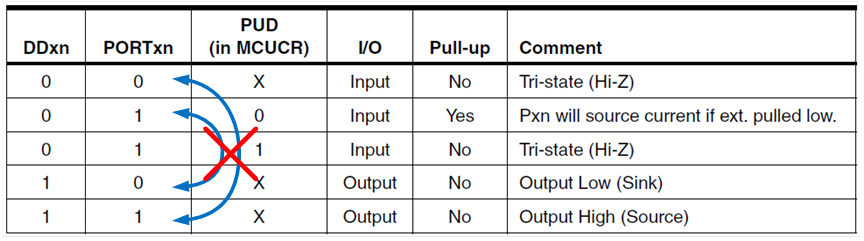

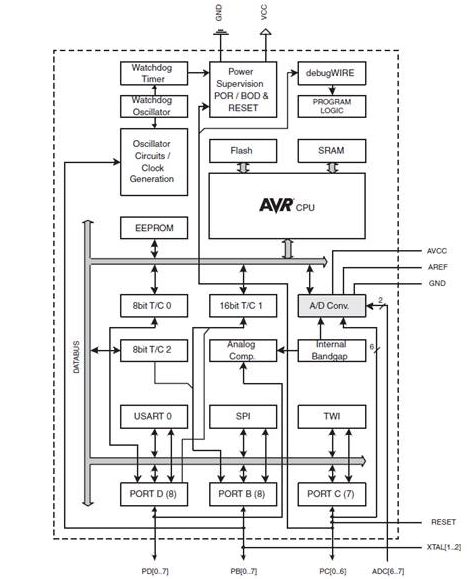

Labs are based on the ATmega32U4 used in the Arduino Leonardo and Nano. The ATmega328P shown here, is used in the Arduino UNO. For instructional purposes, both architectures will be referenced. The ATmega328P is the simpler of the two architectures and the easier to learn.

THE AVR ENGINE

Let’s adopt the analogy used by Charles Babbage when he called his computer an Analytical Engine. For closer look see this article in Wired and ATmega328 Wikipedia page.

INSTRUCTION SET ARCHITECTURE (ISA)

“The Parts of the Engine”

- The Instruction Set Architecture (ISA) of a microprocessor includes all the registers that are accessible to the programmer. In other words, registers that can be modified by the instruction set of the processor.

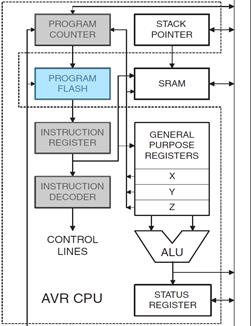

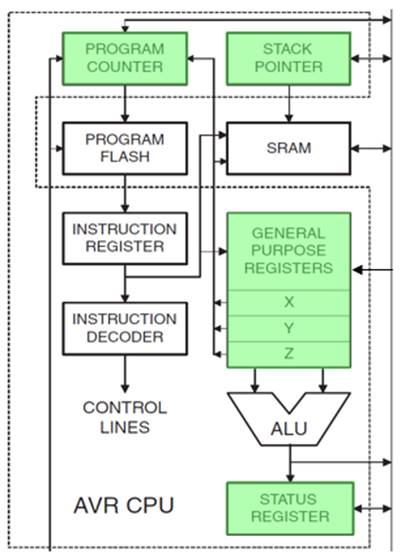

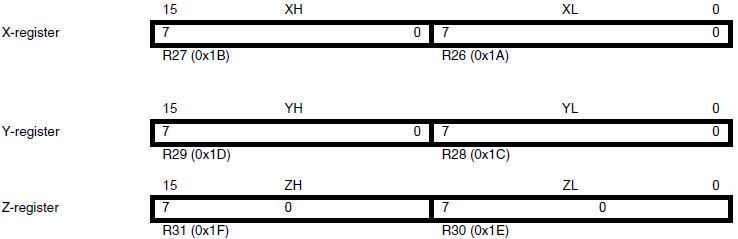

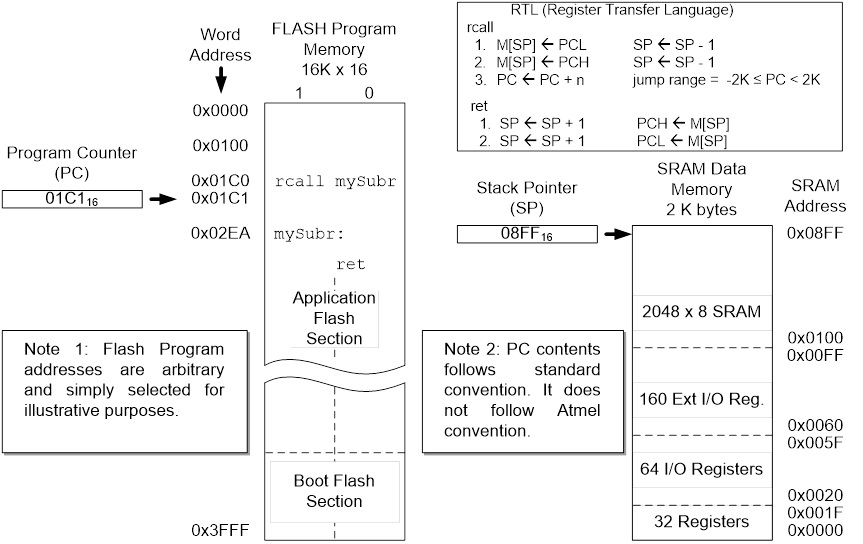

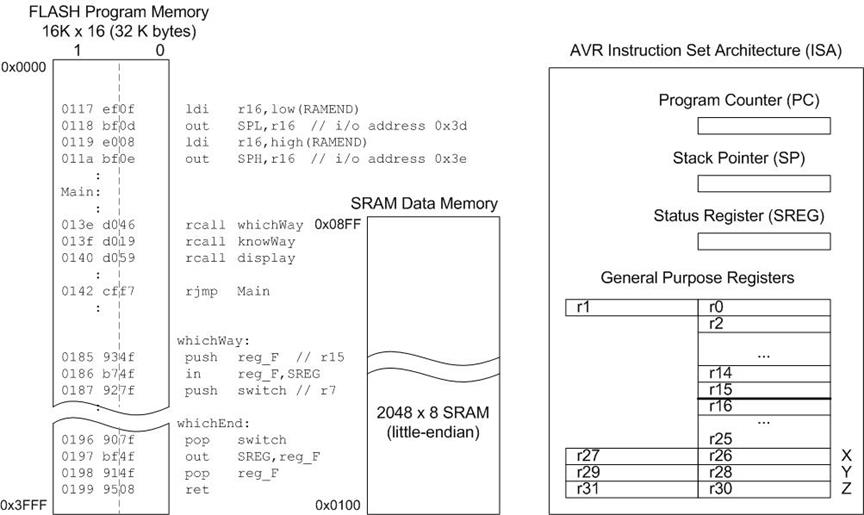

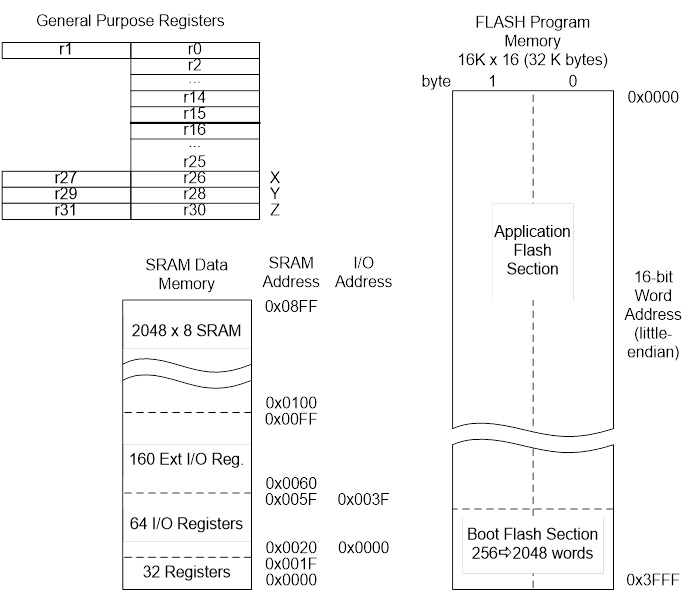

- With respect to the AVR CPU illustrated in Figure 5.2, these ISA registers include the 32 x 8-bit general purpose registers, status register (SREG), the stack pointer (SP), and the program counter (PC).

AVR CPU CORE ARCHITECTURE

“Features of the Engine” Part I

- Reduced Instruction Set Computer (RISC): The instruction set of the computer and target compiler(s) are developed in concert allowing the optimization of both. In this way, a relatively high performance processor can be realized by “reducing” the amount of work any single instruction needs to do; leading to a simpler hardware design (smaller, faster, and cheaper).

8051 Microcontroller ATmega328P Microcontroller cjne A, 0x99, next cmp r16, 0x99

brne next - Mostly 16-bit fixed-length instructions. Instructions have from zero to two operands. Many of today’s RISC microprocessors have up to three operands.

- The Register File of the AVR CPU contains 32 x 8 bit mostly Orthogonal (or identical) General Purpose Registers – instructions can use any register; therefore, simplifying compiler design.

- Load-store memory access. Before you can do anything to data, you must first load it from memory into one of the general-purpose registers. You then use register-register instructions to operate on the data. Finally, you store your answer back into memory.

“Features of the Engine” Part II

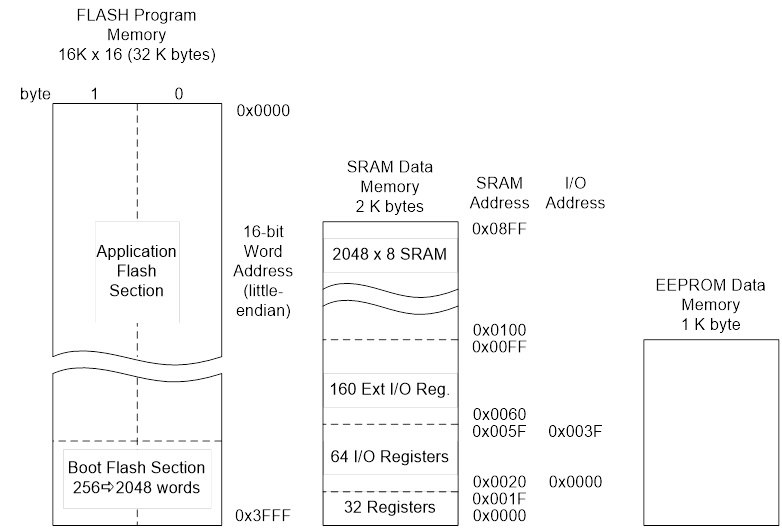

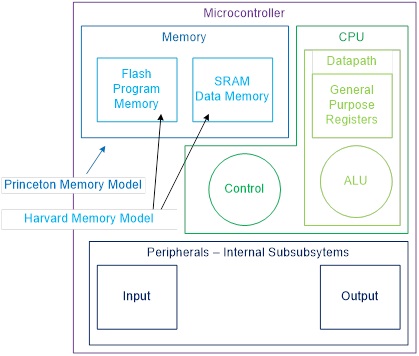

- Modified Harvard memory model: A Harvard memory model separates Program and Data memory into separate physical memory systems (Flash and SRAM) that appear in different address spaces. A Modified Harvard memory model has the ability to read/write data items from/to program memory using special instructions. A Princeton memory model computer has only a single address space, shared by both the program and data.

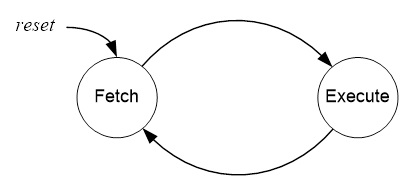

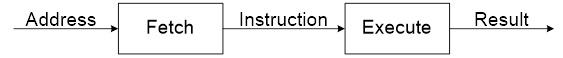

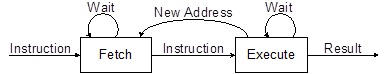

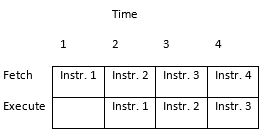

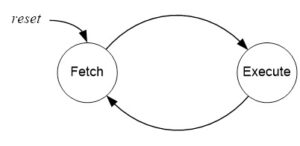

- A Two-stage Instruction Pipeline (fetch and execute) resulting in most instructions being executed in one clock cycle. Consequently, the performance of a 20 MHz processor would approach 20 MIPS (Millions of Instructions Per Second). Compare this with the 8051 Complex Instructions Set Computer (CISC) computer which takes a minimum of 12 clock cycles to execute a single instructions (12 MHz clock = 1 MIPS).

- Simplicity of the computer architecture translates to a faster learning curve and utilization of the machine by the student.

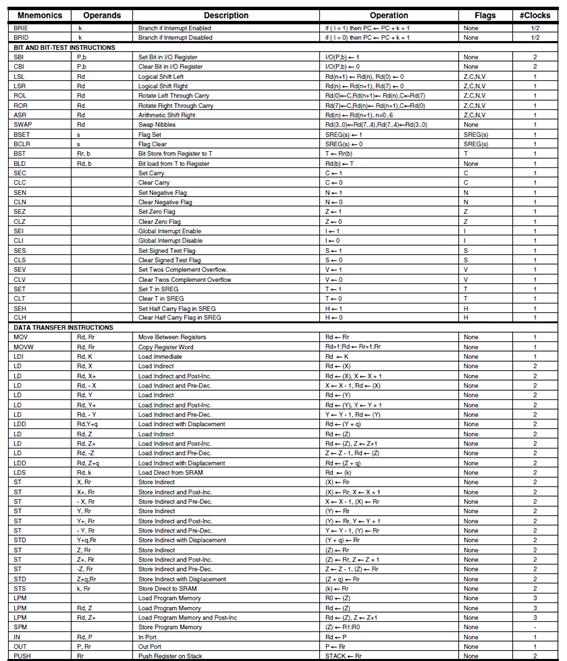

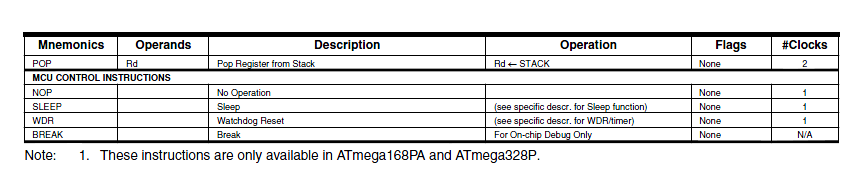

AVR CPU INSTRUCTIONS

“The Language of the Machine”

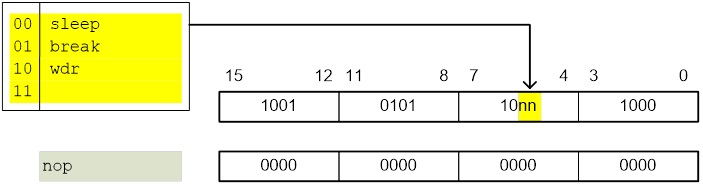

The Instruction Set of our AVR CPU can be functionally divided (or classified) into five (5) categories.

| Data Transfer | |

| Arithmetic and Logical | |

| Bit and Bit-Test | |

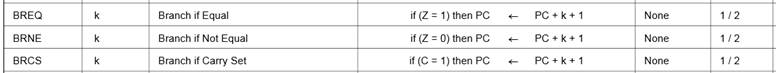

| Control Transfer (Branch Instructions) | “Load the Program Counter” |

| MCU Control | nop, sleep, wdr, break |

- Data Transfer instructions are used to Load and Store data to the General Purpose Registers, also known as the Register File.

-

- Exceptions are the push and pop instructions which modify the Stack Pointer.

- By definition these instructions do not modify the status register (SREG).

- Arithmetic and Logic Instructions plus Bit and Bit-Test Instructions use the ALU to operate on the data contained in the general purpose registers .

- Flags contained in the Status Register (SREG) provide important information concerning the results of these operations.

- For example, if you are adding two signed numbers together, you will want to know if the answer is correct. The state of the overflow flag (OV) bit within SREG gives you the answer to this question (1 = error, 0 no error).

- As the AVR processor fetches and executes instructions it automatically increments the program counter (PC) so it always points at the next instruction to be executed. Control Transfer Instructions allow you to change the contents of the PC either conditionally or unconditionally.

- Continuing our example if an error results from adding two signed numbers together we may want to conditionally (OV = 1) branch to an error handling routine.

INSTRUCTION FETCH AND EXECUTE

“The Basic Cycles of the Engine”

Once built, our computer lives to Fetch and Execute instructions, the bread-and-butter of the computer programmer. For this reason, the programmer views the computer as a vehicle for executing a set of instructions. This perspective is codified by the Instruction Set Architecture (ISA) of the computer.

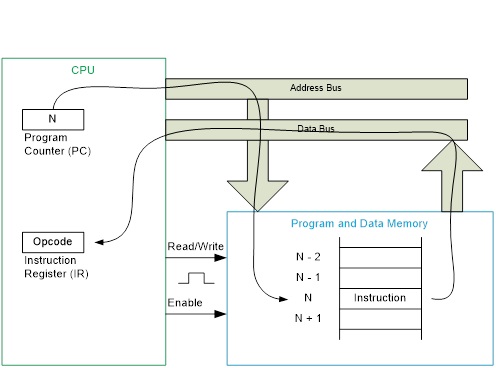

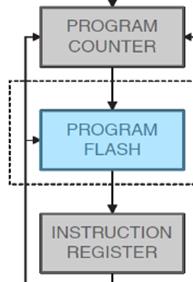

HARVARD VERSUS PRINCETON MEMORY MODEL INSTRUCTION FETCH CYCLE

The five (5) steps required to fetch an instruction on a CPU incorporating the Princeton memory model is provided here. The key difference between the Princeton and Harvard memory model is the physical seperation of program memory from data memory. For embedded systems the program memory is implemented using FLASH memory. With program memory now isolated from data memory, the instruction fetch cycle is reduced to a single (1) step. What is accomplished in that single step is shown in bold.

- The CPU presents the value of the program counter (PC) on the address bus and sets the read control line.

- The Flash program memory looks up the address of the instruction and presents the value on the data bus.

- The value from the data bus is placed into the instruction register and the CPU clears the read control line. The instruction register now holds the instruction to be executed.

- The program counter is incremented so it points to the next instruction to be executed.

- The instruction decoder interprets and implements (executes) the instruction.

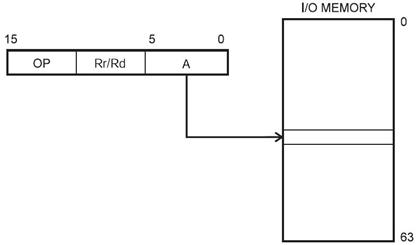

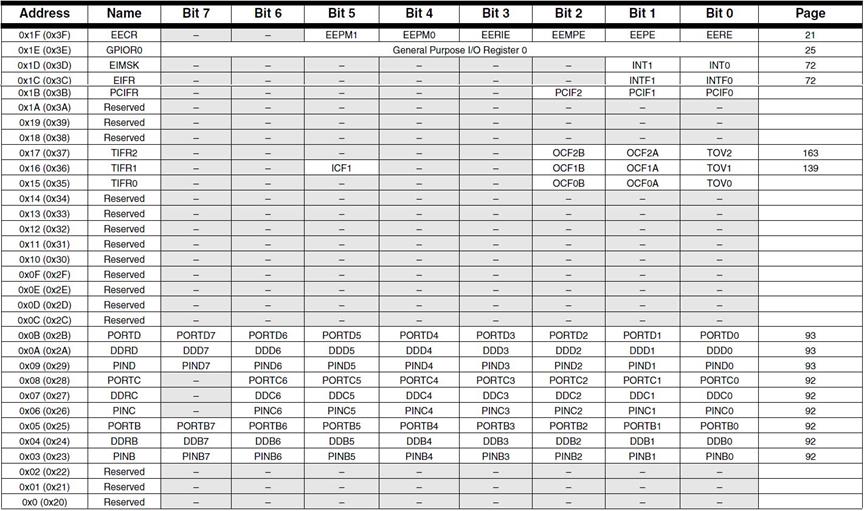

I/O Address Space versus Memory Mapped I/O

- Input and Output ports have traditionally been treated as separate parts of the computer.

- The AVR includes an in instruction to read from an I/O port and an out instruction to write to an I/O port.

- The AVR has 64 I/O registers accessible to these two instructions

Problem: The Atmel ATmega line of Microcontrollers needs more than 64 I/O registers (GPIO, Timers,…)

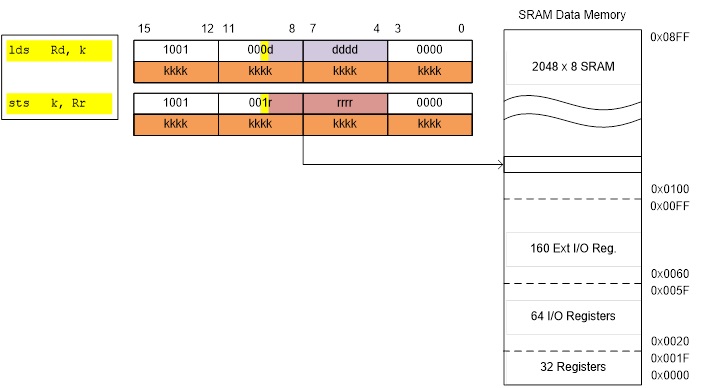

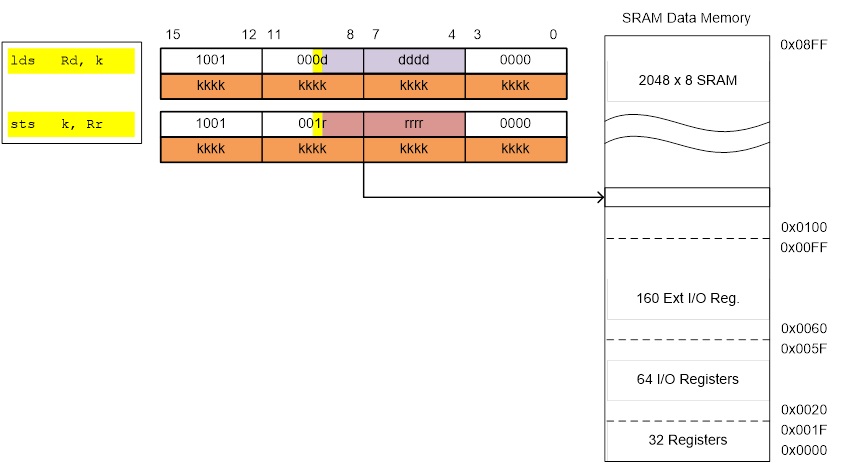

Solution: Instead of looking at computers having 5 basic elements (Input, Output, ALU, CPU, Memory), you can simplify the design to only three (CPU, ALU, and Memory) now allowing the CPU to access 160 “extended” I/O registers using SRAM instructions like lds (load from SRAM) and sts (store to SRAM).

- This was such a powerful technique that Atmel extended the I/O mapping to include the 32 general purpose registers, the original 64 I/O registers, and the 160 extended I/O registers. The overlaying of the I/O address space with the SRAM address space is shown in the next slide.

- A side benefit of the double mapping is the large number of ways of accessing data within SRAM (addressing modes) versus the limited number of instructions and addressing modes available for accessing the original 64 I/O registers (i.e., in, out).

- It is very important to realize that I/O registers are not contiguous within the address space (I/O or SRAM). The mapping is simply a convenient way of accessing registers physically located in diverse locations within the Silicon chip.

Atmel ATmega328P Memory Model

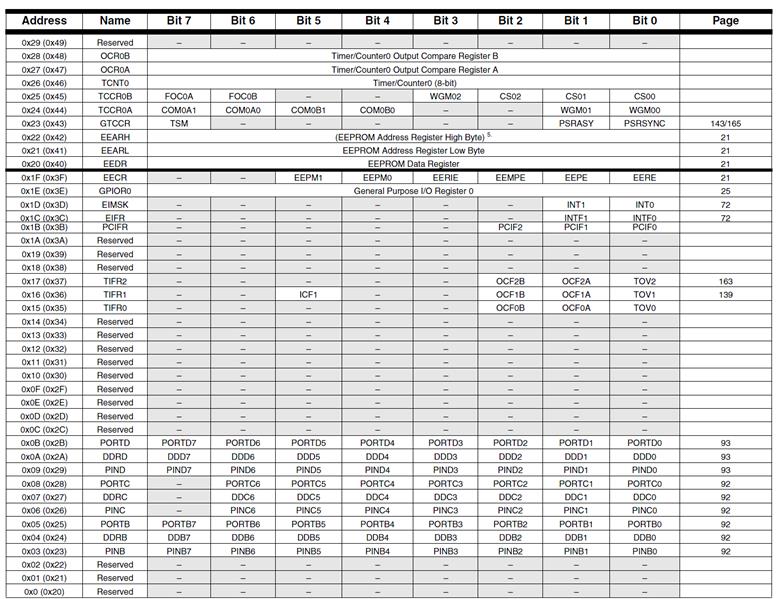

ATMEGA328P I/O MEMORY MAP

Appendix

APPENDIX A PROCESSOR CONTROL AND DATAPATH

| Control | Datapath |

| Component of the processor that commands the datapath, memory, data, I/O devices according to the instructions of the memory | Components of the processor that perform arithmetic operations and holds data |

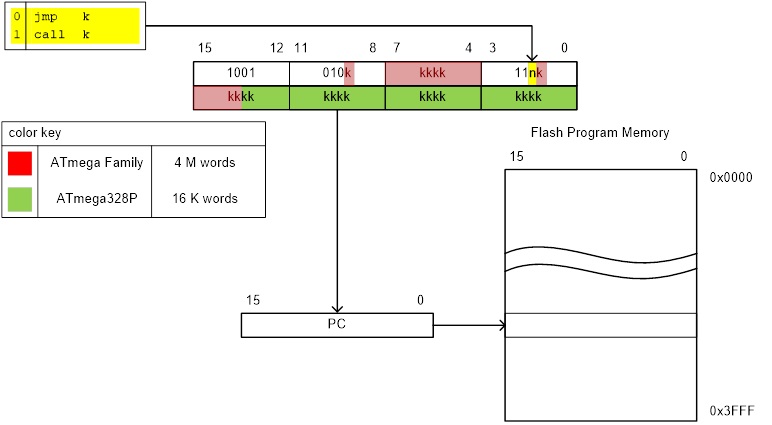

APPENDIX B CALCULATING THE LAST ADDRESS

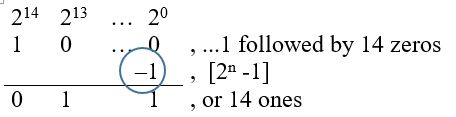

Given a 16K word (2 bytes / word) memory, what is the last address, in hexadecimal?

- The range of memory addresses, like an unsigned number, is from 0 to 2n – 1

- We are given the size of our memory in decimal as 16K10. So the first step is to convert this number to a power of 2.

16K10 = 24 * 210 = 214, which in binary would be… - Which then can directly be expressed as a binary number.

- So the answer is 0x3FFF

- As a short-cut, if you can convert the memory size to a power of 2, the exponent equals the number of 1 in the answer. By dividing the exponent by 4, you have the number of hex digits which are F (11112), with the remainder giving you the most significant hex digit. In our example 4 goes into 14, 3 times with a remainder of 2, where 2 ones (00112) equal hexadecimal 316.

APPENDIX C I/O ADDRESS SPACE VERSUS MEMORY MAPPED I/O

Reading: Your textbook covers memory organization in Section 0.3 “Semiconductor Memory” and I/O Mapping in Section 2.2 “The AVR Data Memory.” The following material covers mapping of the I/O address space in a slightly different way. The material was provided in bullet form earlier in this document.

From Charles Babbage’s Analytical Engine to Dr. Jon Von Neumann’s paper on the EDVAC computer, Input and Output have been treated as separate parts of the computer. Input and Output parts of your PC include the keyboard, mouse, printer, display, etc. To support these “peripheral” devices many microprocessors include a separate I/O address space and instructions for working with the registers contained used to control and access data provided by the peripheral device. For the AVR microcontroller you read an I/O register using an in instruction and write using the out instruction. When Atmel adopted the AVR architecture, they discovered that the 64 I/O registers accessible to these two instructions was insufficient for all the peripheral devices that they were planning on adding to the ATmega line of Microcontrollers. Specifically, they added 160 “extended” I/O registers. However, the AVR microprocessor was only designed for 64 I/O registers. To solve this problem, Atmel turned to an alternative way of working with I/O devices pioneered by Motorola and the 6800 family of processors (among others). Motorola realized that there was no reason to treat input and output devices any different from memory. Now instead of looking at computers having 5 basic elements (Input, Output, ALU, CPU, Memory), you could simplify the design to only three (CPU, ALU, and Memory). Now accessing the 160 “extended” I/O registers was accomplished using SRAM instruction like lds (load from SRAM) and sts (store to SRAM). This was such a powerful technique that Atmel extended the I/O mapping to include the 32 general purpose registers, the original 64 I/O registers, and the 160 extended I/O registers. The overlaying of the I/O address space with the SRAM address space is shown in the next section.

A side benefit of the double mapping is the large number of ways of accessing data within SRAM (addressing modes) versus the limited number of instructions and addressing modes available for accessing the original 64 I/O registers.

It is very important to realize that I/O registers are not contiguous within the address space (I/O or SRAM). The mapping is simply a convenient way of accessing registers physically located in diverse locations within the Silicon chip.

APPENDIX D A BRIEF HISTORY OF THE COMPUTER

4,000 to 3,000 BC Abacus (+, -, *, /)

- The abacus is an instrument used to perform arithmetic calculations. The positions of beads on a set of wires determine the value of the digit. Romans called these beads calculi the plural of calculus, meaning pebble. This Latin root gave rise to the word calculate. In one contest the Abacus easily won over a mechanical calculator. The abacus is still used in China, Japan, and Korea.

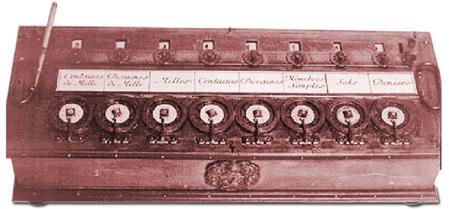

1642 Blaise Pascal Mechanical Calculator (+, -)

- Designed at the age of 20. Rotating wheel mechanical calculator with automatic carry between digits on addition and subtraction of decimal digits (like the odometer in a car). In 1671 Baron von Leibnitz created a calculator, which could add, subtract, and multiply.

- A Human Computer with a mechanical calculator can execute 500 operations a day

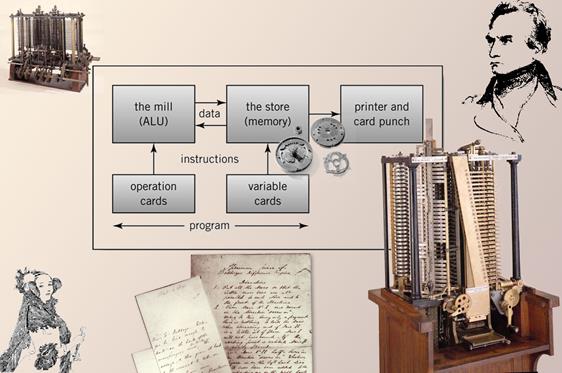

1833 Charles Babbage and the Analytical Engine

- Conceived by Babbage, the engine established the basic principles upon which modern general-purpose digital computers are constructed. This mechanical machine performed instructions dictated by punched cards, with the variable values being determined by a second set of cards. The punched cards came from Joseph Marie Jacquard’s loom, where they controlled the operation of the weaving machines in 1812.

- Neither the Analytical Engine or Difference Engine (1820), a special purpose computer designed to solve polynomial expressions (ex. N2 + N + 41), were ever entirely completed by Babbage known as “the irascible genius.” The difference engine has recently been built as shown here.

1843 Ada Byron and the First Computer Program

- Ada Byron, Lady Lovelace, was one of the most picturesque characters in computer history. Augusta Ada Byron was born December 10, 1815 the daughter of the illustrious poet, Lord Byron. Ada was brought up to be a mathematician and scientist. It was at a dinner party at Mrs. Somerville’s that Ada heard in November 1834, Babbage’s ideas for a new calculating engine, the Analytical Engine. Ada, in 1843, married to the Earl of Lovelace and the mother of three children under the age of eight, wrote an article describing Babbage’s Analytical Engine. Lady Lovelace’s prescient comments included her predictions that such a machine might be used to compose complex music, to produce graphics, and would be used for both practical and scientific use. When inspired Ada could be very focused and a mathematical taskmaster. Ada suggested to Babbage writing a plan for how the engine might calculate Bernoulli numbers. This plan, is now regarded as the first “computer program.” Like her father, she died at 36, Ada anticipated by more than a century most of what we think is brand-new computing.

Source: http://www.scottlan.edu/lriddle/women/love.htm

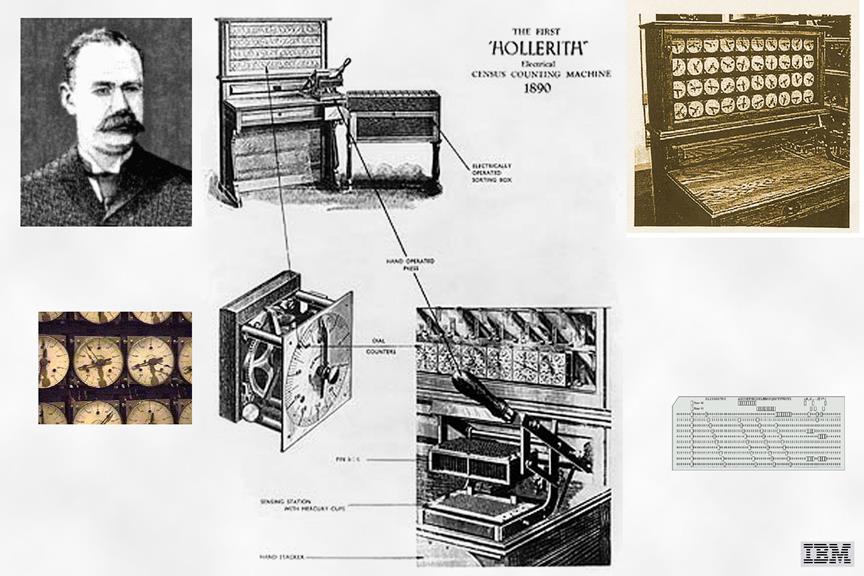

1890 Herman Hollerith and the Census Counting Machine

- Hollerith developed punched cards for tabulating equipment used in the 11th census of the United States. Cards contained 288 locations, size of dollar bill in order to save on tooling. Contact brushes completed electrical circuits allowing the system to do: counting, sensing, punching, and sorting. Started Tabulating Machine Company, which turned into the Computer-Tabulating-Recording Company, which turned into the International Business Machine Corporation (IBM) in 1924.

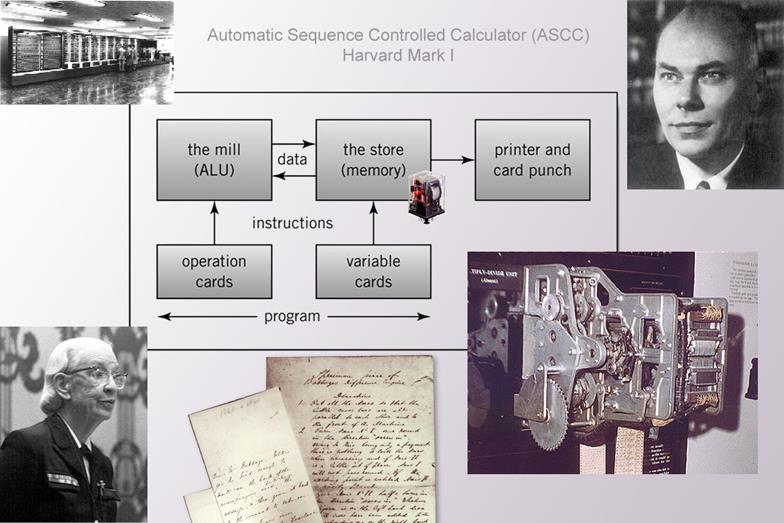

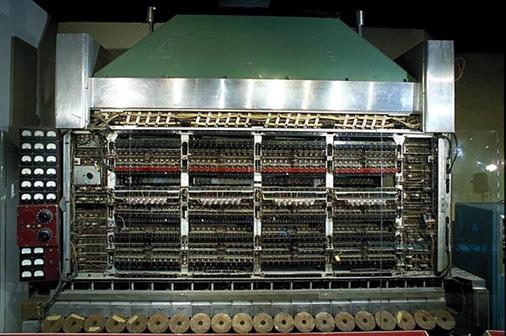

1937 Harvard Mark I

- Howard Hathaway Aiken at Harvard proposed to IBM the Mark I or Automatic Sequence Controlled Calculator — this was to be the first large-scale calculator. Very similar to the Analytical engine, the machine used a combination of electromechanical devices, including many relays. It went to work in 1944 calculating with numbers of 23 digits and computer products of 46-digit accuracy. It received its instructions from perforated tape, from IBM cards, and from the mechanical setting of 1,440 dial switches. Output was either by IBM cards or by typing columns of figures on a roll of paper. The Mark I could perform one division per minute. The machine was in operation for many years, generating many tables of mathematical functions (particularly Bessel functions), and was used for trajectory calculations in World War II.

1943 Electronic Numerical Integrator and Computer (ENIAC)

- Engineers J. Presper Eckert and John W. Mauchly created the ENIAC at the Moore School of Engineering of the University of Pennsylvania between 1943-1946. Built in war time secrecy for the army ordnance department, the ENIAC was designed to do Trajectory calculations. Containing 18,000 vacuum tubes, each accumulator using 100 vacuum tubes arranged as 10 columns of 10 tubes each, the ENIAC could add two 10-digit numbers (the size of ENIAC’s decimal accumulators) in 200 microseconds. Thirty thousand (30,000) times faster than the Mark I. The ENIAC was programmed by patch board and switches. The ENIAC was later moved at a cost of $100,000 to the Ballistic Research Laboratories at the Aberdeen Proving Ground.

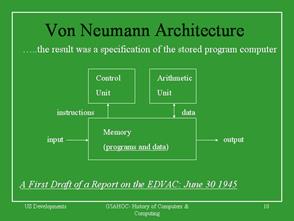

1945 Dr. John Von Neumann and the Electronic Discrete Variable Computer (EDVAC)

- EDVAC was the first general-purpose stored program binary electronic (vacuum tube) computer. Completed in 1950 after the EDSAC thus it was not the first operational stored program computer. The technical work done on the EDVAC was by Eckert and Mauchly, Notable the Ultrasonic (or Supersonic) Delay Line, with the logical organization done by Von Neumann, Burke, and Goldstine.

- This computer was the blueprint for most modern day computer systems having in it the 5 principle organs that make up almost all modern day computers. Input, Output, Arithmetical, Central Control, Memory (storing both the numerical as well as the instructional information for a given problem), Eckert as well as others left before the EDVAC was ever completed. Architecturally the EDVAC is classified as a general purpose four address computer.

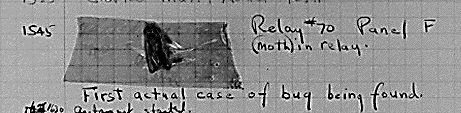

1947 The First Computer Bug

- American engineers have been calling small flaws in machines “bugs” for over a century. Thomas Edison talked about bugs in electrical circuits in the 1870s. When the first computers were built during the early 1940s, people working on them found bugs in both the hardware of the machines and in the programs that ran them.

- In 1947, engineers working on the Mark II computer at Harvard University found a moth stuck in one of the components. They taped the insect in their logbook and labeled it “first actual case of bug being found.” The words “bug” and “debug” soon became a standard part of the language of computer programmers.

1951 John Von Neumann and Princeton’s IAS (Institute for Advance Study) Machine

- Designed to develop a world weather model, the IAS machine incorporated most of the general concepts of parallel binary stored-program computers. That is it used random access memory or parallel memory, CRTs. One address computer.

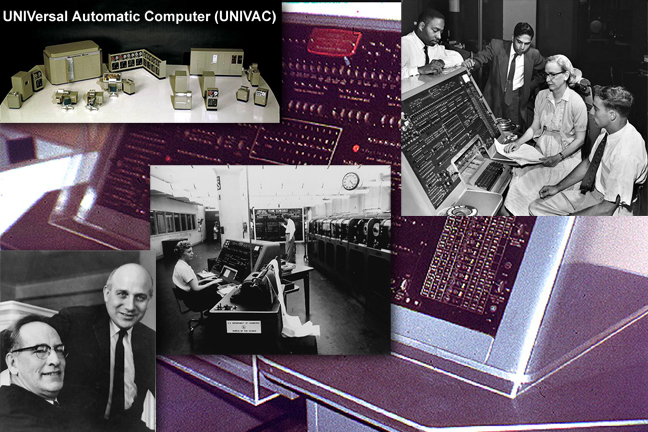

1951 Eckert and Mauchly and the UNIVAC I

- Soon after the formal dedication of ENIAC computer, J. Presper Eckert and John W. Mauchley’s left the University of Pennsylvania to start their own business. Early orders from U.S. government agencies and other potential customers were not enough to keep the young Eckert-Mauchley Computer Corporation alive, and Remington Rand agreed to purchase the firm in 1950. Work on the UNIVAC I (Universal Automatic Computer) went forward, and the first commercially available electronic (vacuum tube) digital computer was delivered to the Bureau of the Census in early 1951. By 1957, some 46 copies of the machine had been installed at locations ranging from the David Taylor Model Basin of the U.S. Navy Bureau of Ships, to Pacific Mutual Life Insurance Company, to the offices of the Commonwealth of Pennsylvania.

- The UNIVAC, like the ENIAC, had vacuum tube circuit elements. There also were some 18,000 crystal diodes. Central memory was handled in acoustic delay-line tanks, which were used in several early computers. UNIVAC also had an external magnetic tape memory, as well as magnetic tapes used in input and output. Users of UNIVAC played an important role in the development of programming languages. Source: Smithsonian Computer History Collection

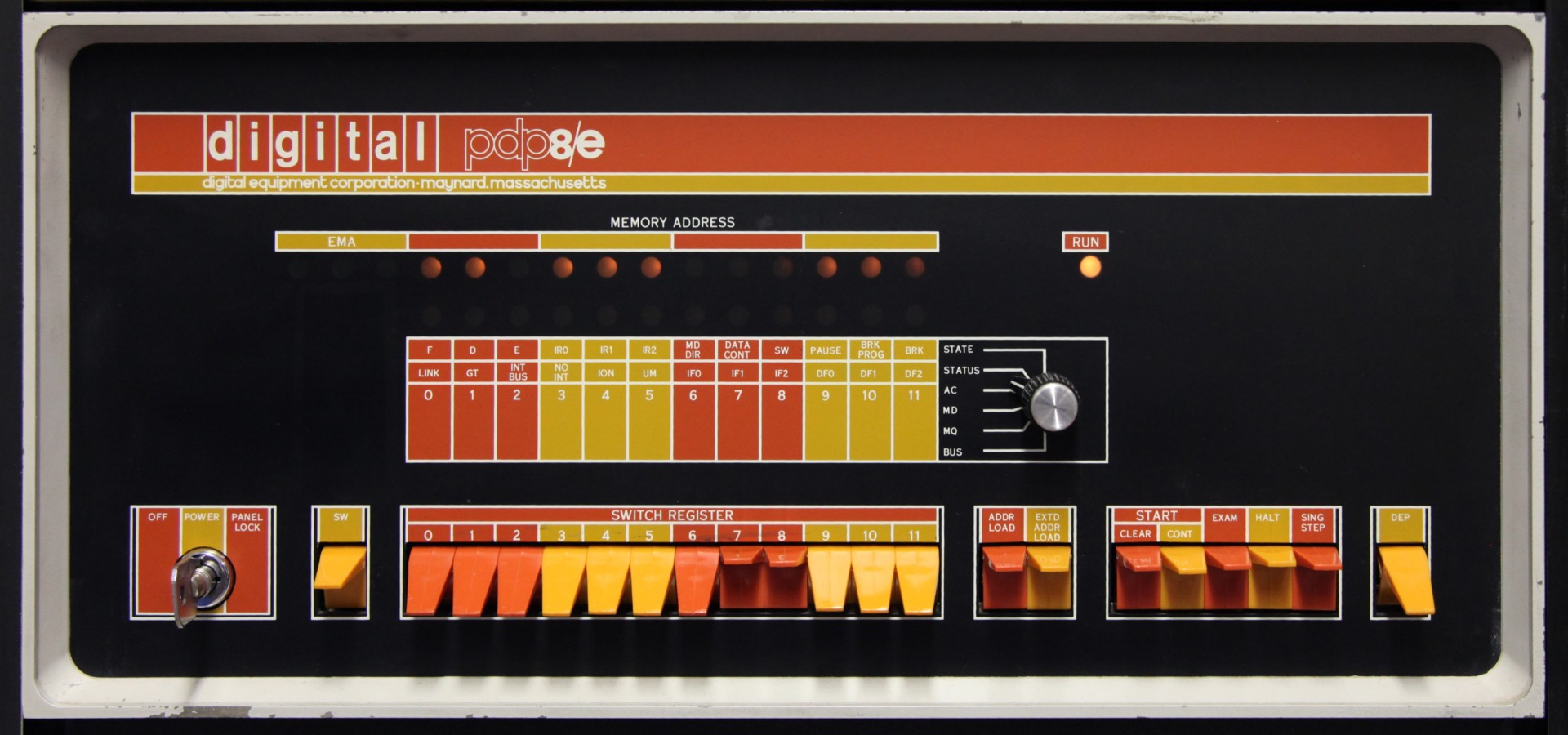

1965 Digital Equipment Corporation (DEC) PDP-8

- Designed using Integrated Circuits, DEC sold the first PDP-8 for only $18,000. Later versions of this machine that incorporated improvements in electronics appeared over the next decade. These became steadily smaller and cheaper, triggering a rush of new applications in which the computer was embedded into another system and sold by a third party (called an Original Equipment Manufacturer, or OEM). Some machines were specifically designed for time sharing and for business applications. Ultimately over 50,000 PDP-8’s were sold (excluding those embedded as single chips into other systems) bringing computers into the laboratory and the manufacturing plant’s production line, and thus the minicomputer industry was born. (read “The Sole of a New Machine”).

The x86 isn’t all that complex — it just doesn’t make a lot of sense

Mike Johnson

Leader of the 80×86 Design at AMD

Microprocessor Report (1994)

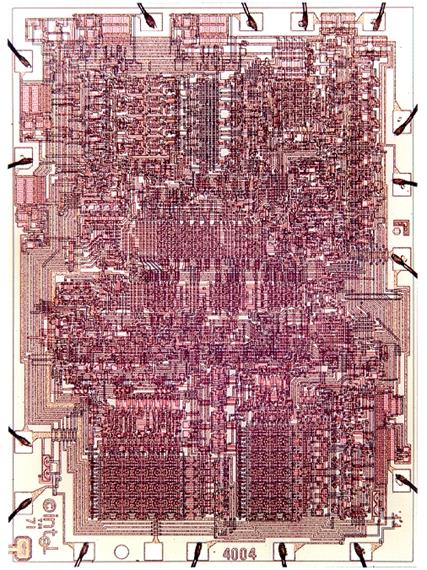

June 1969 to April 1971 Ted Hoff and Intel 3-chipset 4004

- Intel, a company founded in 1968, is asked by Busicom of Japan to design a custom LSI calculator chip-set. Intel discovers design will take 11 36-40 pin IC packages and proposes a creative alternative. Ted Hoff, at Intel, had been working with the PDP-8 min-computer and proposed to Busicom that a general purpose LSI chip-set be designed that could be programmed to be a calculator or for other applications. We are so used to using computers, that the genus of this step can escape us. The traditional solution was to design what you wanted using logic gates. What Ted Hoff envisioned was a wholly different approach. You design a simple CPU and taught it using software to do what you want. Today these computers are known a microcontrollers and embedded systems. Publicly announced on November 1971.

Nov 1969 to Jan 1972 Vic Poor and the Intel 8008

- Vic Poor of Datapoint Corporation of San Antonio, Texas (manufacturers of “intelligent terminals” and small computer systems) along with Cogar and Viatron engineers design a very elementary computer, and put under contract Intel and Texas Instruments to implement the design on a single logic chip. Intel succeeded, but their product executed instructions approximately ten (10) times as slowly as Datapoint had specified and way behind schedule (work had been stopped by Intel to complete the Busicom chip-set.); so Datapoint declined to buy it, and built their own product using existing logic components. And thus Intel holding a computer-like logic device (whose development had been paid for) marketed the Intel 8008 and the microcomputer industry was born.

1975 John Cocke and the IBM 801

- The first (Reduced Instruction Set Computer) RISC machine was developed as part of the IBM 801 Minicomputer Project. John Cocke contributed many detailed innovations in the 801 processor and associated optimizing compiler, and is considered the “father of RISC architecture.”

- “John’s concept of the RISC resulted from his detailed study of the trade-offs between high performance machine organization and compiler optimization technology. He recognized that an appropriately defined set of machine instructions, program controls, and programs produced by a compiler — carefully designed to exploit the instruction set — could realize a very high performance processor with relatively few circuits. Critical to the success of RISC was the concept of an optimizing compiler able to use the reduced instruction set very efficiently and maximize performance of the machine.”

Source: http://domino.watson.ibm.com/comm/pr.nsf/pages/news.20020717_cocke.html

1976 Intel i8748

- Prior to 1976 small board computers (SBCs) were designed around microprocessor chips, like the 8080. These SBCs included all the features needed to implement a very simple computer system. These SBCs, of which the D2 by Motorola, KIM-1 by MOS Technology, and SDK-85 by Intel are the most memorable, quickly found their way into design labs at colleges, universities, and electronic companies. By adding peripheral cards these SBCs could read sensors and control actuators. In 1976 Intel put all of the features found on an SBC and parts of the peripheral cards into one chip known as the i8748. With over 17,000 transistors the i8748 was the first device in the MCS-48 family of microcontrollers. This IC, and other MCS-48 devices, quickly became the de facto industrial standard in control-oriented applications. Soon MCS-48 devices were replacing electromechanical components in many modern appliances.

1980 Intel 8051

- With over 60,000 transistors, the power, size, and complexity of microcontrollers moved to the next level with Intel’s introduction of the 8051, the first device in the MCS-51 family of microcontrollers. In a bold move, Intel allowed other manufacturers to make and market code-compatible variants of the 8051. This step led to its general acceptance by the engineering community as the de facto standard in microcontroller architectures.

1996 Atmel AVR

- AVR is a moniker for a family of Atmel 8-bit RISC microcontrollers. The AVR is a Modified Harvard architecture machine with program and data stored in separate physical memory systems that appear in different address spaces. The AVR architecture was conceived by Alf-Egil Bogen and Vegard Wollan at the Norwegian Institute of Technology (NTH). When the technology was sold to Atmel, the internal architecture was further developed by Alf and Vegard at Atmel Norway, a subsidiary of Atmel founded by the two architects. The name AVR sounds cool and does not stand for anything.

Source: http://en.wikipedia.org/wiki/Atmel_AVR

APPENDIX E CLASSIC COMPUTER ARCHITECTURE

As we discovered in our short history lesson, computers are designed to meet a specific set of requirements. In the early days, these requirements were to meet some military, science, civil, or commercial need. For the military, it was predominately the calculation of ballistic tables; for science to calculate the motion of the planets or the weather. For civil keeping track of people and commercial keeping track of the money. To meet these requirements the computer was conceived and described by its (1) hardware components and (2) the instructions it could execute. The former, for all modern day computers, were codified by Von Neumann in his landmark paper describing the architecture of the EDVAC computer.

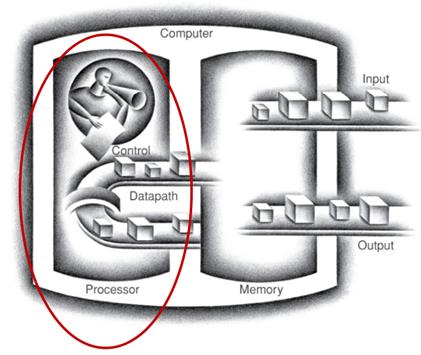

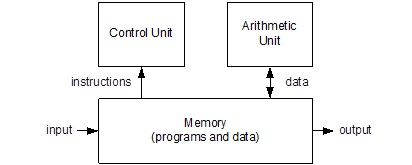

Von Neumann’s paper describes a computer architecture having five basic components: Input, Output, Memory, Control, and Arithmetical.

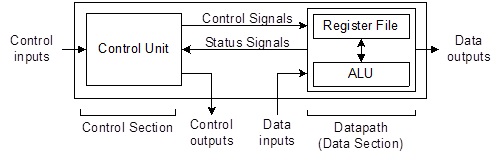

For this class we will Reparation these elements as discussed in the next section and defined in Figure 1-3. An important component of this new viewpoint is the central processing unit (CPU) which will be divided into a Control and a Datapath element as shown in the Figure 1-2. Atmel literature uses the term microcontroller unit (MCU) in place of the more generic central processing unit. In this course the two terms are considered synonymous.

Classic Microcontroller Architecture

The CPU is divided into a Control and a Datapath element as shown in the Figure 1-2. The Control Unit contains combination logic and translates the instructions held in the instruction register (not shown) into the control signals needed to execute the instruction. The data path contains the General Purpose Registers (technically known as the Register File) and the Arithmetic and Logic Unit (ALU). The Datapath includes a few other registers which we will learn about shortly.

The integration of the program and data memory described by Von Neumann is today known as the Princeton memory model. The architecture of our AVR processor separates these two types of memory into Flash Program Memory and Static Random Memory (SRAM). This separation of program and data memory more resembles the Harvard Mark I computer, than the EDVAC computer, and is therefore known as the Harvard memory model.

The input and output functions of Figure 1-1 will be treated together and simply called input/output (I/O). For microcontrollers, the term I/O includes all the Peripherals (Parallel I/O, Counter/Timers, etc.) supported by a particular model of microcontroller, in our case the ATmega328P.

For this class the Von Neumann architecture is thus repartitioned into five basic blocks: Flash Program Memory, SRAM Data Memory, Control Unit, Datapath, and Input-Output.

APPENDIX F ATMEGA328P ARCHITECTURAL OVERVIEW

Reading: Section 5.1 Overview plus Atmega8 Block Diagram

Clock

- ATmega Family – Up to 20 MHz

- Arduino Duemilanove – 16 MHz (ATmega328P)

- ALU – On-chip 2-cycle Hardware Multiplier

Memory

- ATmega Family – Up to 256 KBytes Flash, 4K Bytes EEPROM and 8K Bytes SRAM.

- ATmega328P – 32 KBytes Flash, 1K Bytes EEPROM, and 2K Bytes SRAM

- Self-Programming Flash memory with boot block (ICSP header)

Peripheral Subsystems

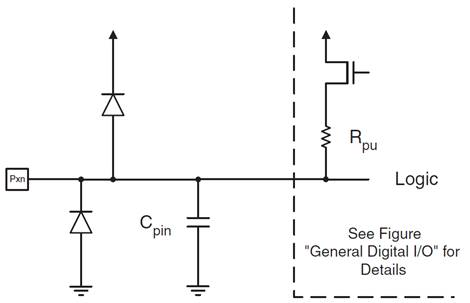

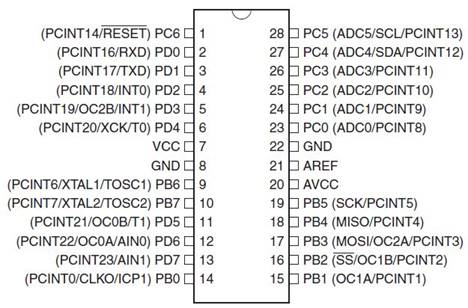

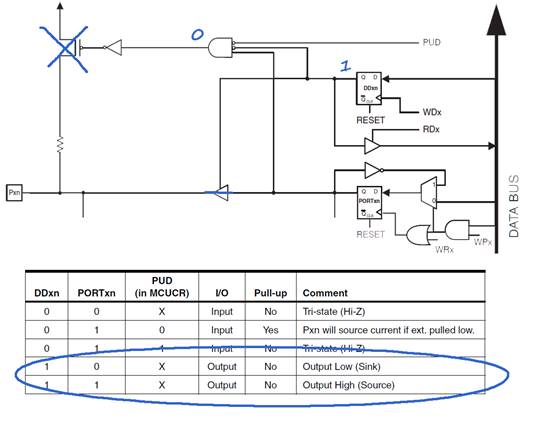

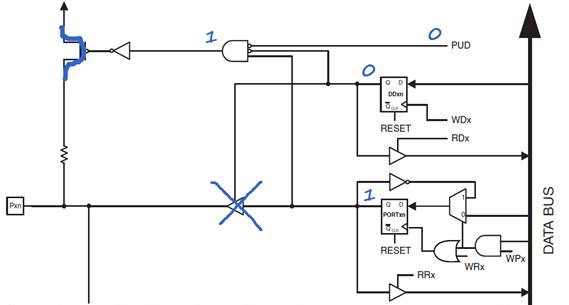

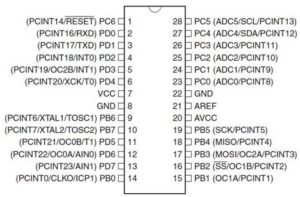

- Two 8-bit (PORTB, PORTD), plus One 7-bit (PORTC) General Digital I/O Ports

- Programmable Serial USART, Master/Slave SPI Serial Interface.

- Byte-oriented 2-wire Serial Interface (TWI) is Philips I2C compliant.

- Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Six PWM Channels

- 8-channel 10-bit A/D converter with up to x200 analog gain stage.

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-Chip Debug through JTAG or debugWIRE interface.

Other Features

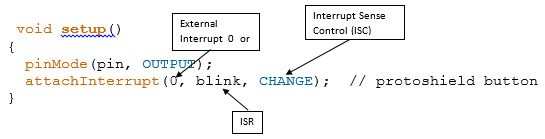

- External and Internal Interrupt Sources with 2 instruction words/vector

Note

- In the following Block Diagram, Power (Vcc), Ground (GND), and the clock input (XTAL) are present but not shown.

APPENDIX G MICROPROCESSOR VERSUS MICROCONTROLLER

APPENDIX H TWO-STAGE INSTRUCTION PIPELINE

Pipelining: A technique that breaks operations, such as instruction processing or bus transactions, into smaller distinct stages or tenures (respectively) so that a subsequent operation can begin before the previous one has completed.

From the Atmel ATmega328P Data Sheet Chapter 6 AVR CPU Core, Section 6.1 Overview and with respect to Figure 6-1 Block Diagram of the AVR Architecture

“In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.”

A pipeline stage begins and ends with a register; controlled by a clock. Between the register(s) is combinational logic. Although counter-intuitive, Flash program memory can be viewed as combinational logic with an address generating a word of data. With respect to our AVR architecture (Figure 6-1) the two registers of interest are the Program Counter (PC) and the Instruction Register (IR). Without pipelining these two registers in the control unit (PC, IR) would require two clock cycles to complete a basic computer operation cycle. Specifically, an instruction is (1) fetched and then (2) executed.

For most instructions, especially one based on a modified Harvard memory model, program memory is not accessed during the execution cycle. This memory down time could be used to fetch the next instruction to be executed, in parallel with the execution cycle of the current instruction. Here then is an opportunity for pipelining! Figure 10.2 illustrates the idea. The pipeline has two independent stages. The first stage fetches an instruction and places it in the Instruction Register (IR), while the second stage is executing the instruction. This two-stage instruction pipeline is also called instruction prefetch can be found in some of the earliest microprocessors including the Intel 8086

For our RISC architecture most instructions are executed in a single cycle (also known as elemental instructions). In this perfect world where all instructions take one cycle to fetch and one cycle to execute, after an initial delay of one cycle to fill the pipeline, known as latency, each instruction will take only one cycle to complete.

Forgetting for now the circuit delays attendant with implementing the pipeline (for example the latch), and other complicating issues, our performance would be twice that of a non-pipelined design.

APPENDIX I ATMEGA328P INSTRUCTION SET

The Instruction Set of our AVR processor can be functionally divided (or classified) into the following types:

- Data Transfer Instructions

- Arithmetic and Logic Instructions

- Bit and Bit-Test Instructions

- Branch (Control Transfer) Instructions

- MCU Control Instructions

Addressing Modes: Working with AVR’s Load-Store RISC Architecture

READING

The AVR Microcontroller and Embedded Systems using Assembly and C

by Muhammad Ali Mazidi, Sarmad Naimi, and Sepehr Naimi

Sections: 2.3, 6.2

Table of Contents

LOAD-STORE INSTRUCTIONS AND THE ATMEGA328P MEMORY MODEL

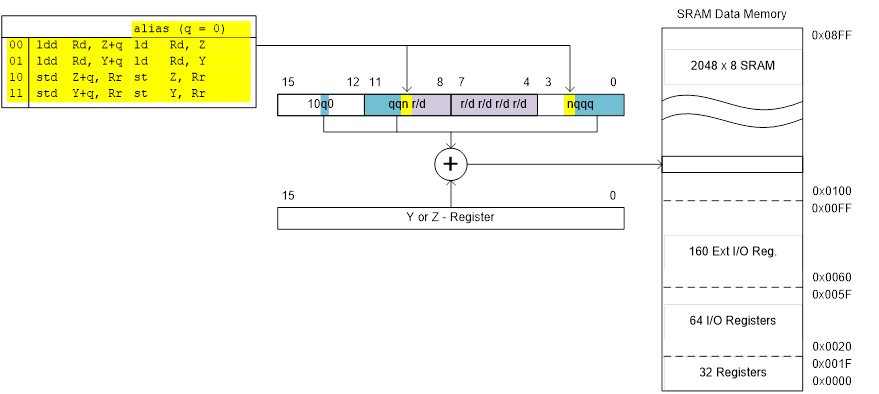

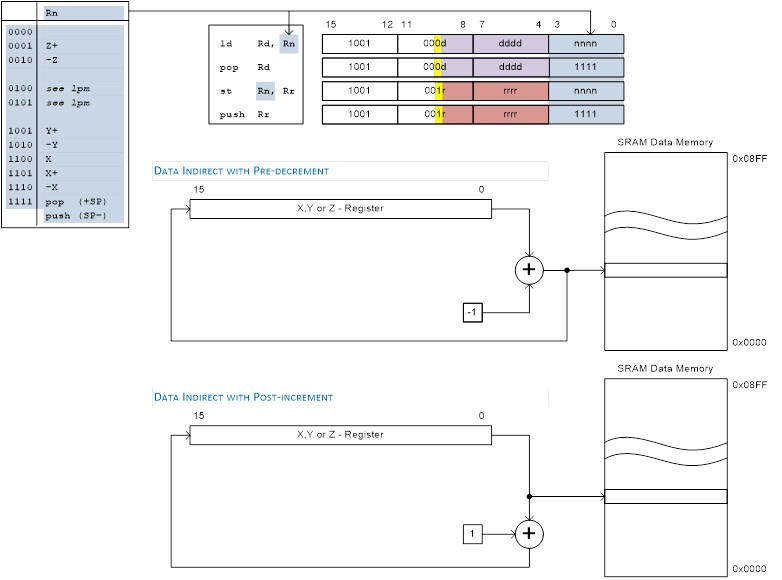

When selecting an addressing mode you should ask yourself where is the operand (data) located within the memory model of the AVR processor and when do I know its address (assembly time or at run time).

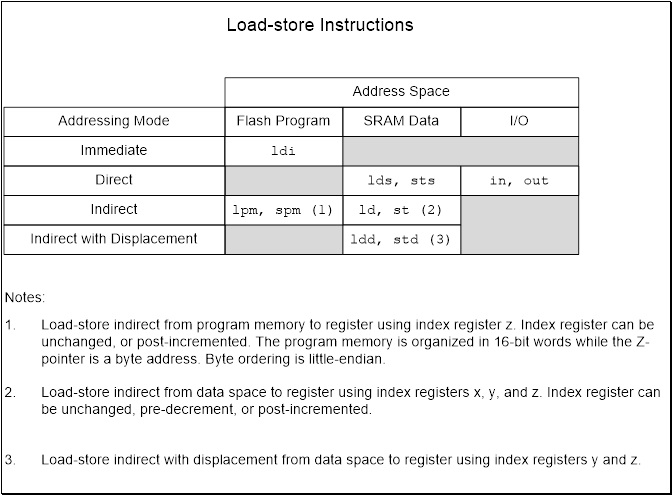

LOAD-STORE INSTRUCTIONS AND ADDRESSING MODES

- When loading and storing data we have several ways to “address” the data.

- The AVR microcontroller supports addressing modes for access to the Program memory (Flash) and Data memory (SRAM, Register file, I/O Memory, and Extended I/O Memory).

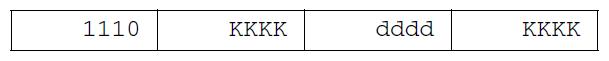

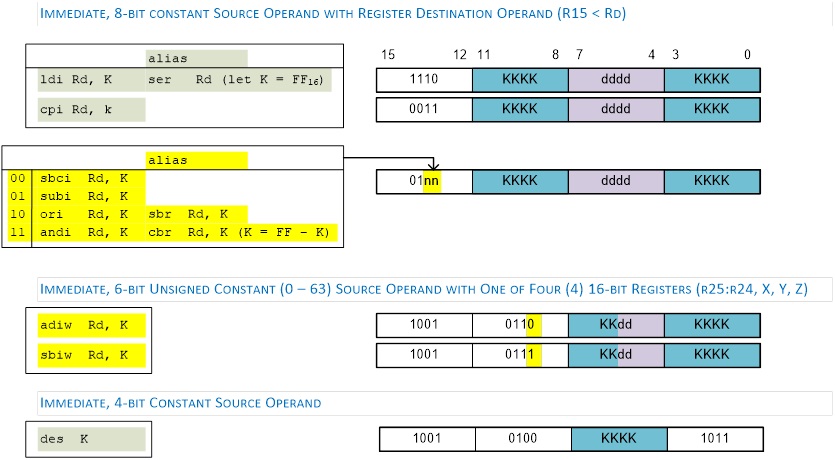

IMMEDIATE

- Data is encoded with the instruction. Operand is therefore located in Flash Program Memory. This is why technically our memory model is a Modified Harvard.

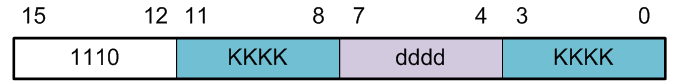

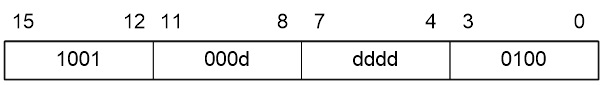

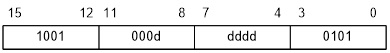

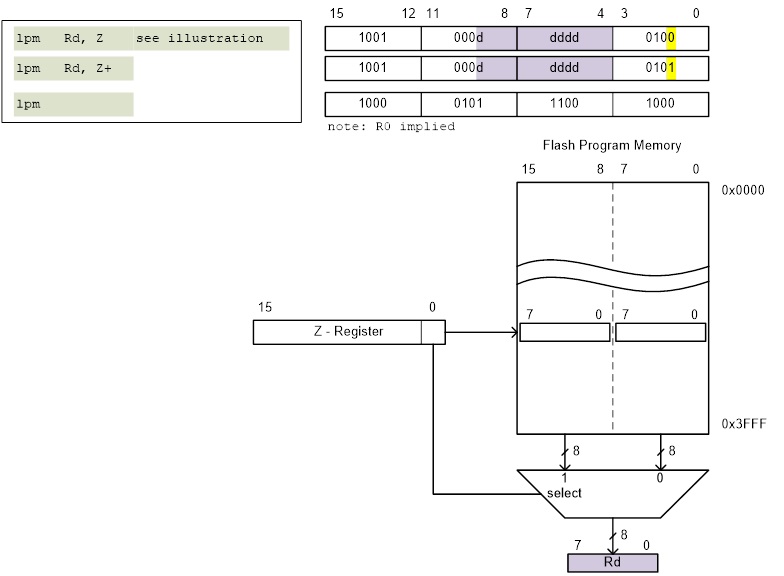

ldi r16, 0x23 // where ldi = 1110, Rd = 00002, and constant K = 001000112

- Notice that only four bits (dddd) are set aside for defining destination register Rd. This limits us to 24 = 16 registers. The designers of the AVR processor chose registers 16 to 31 to be these registers (i.e., 16 ≤ Rd ≤ 31).

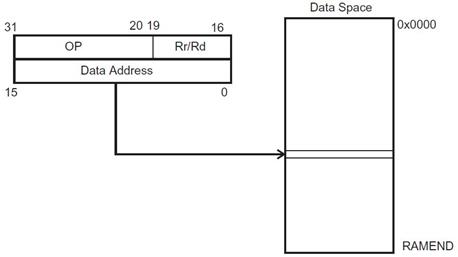

DIRECT

lds r16, A

sts A, r16

Within the AVR family there are two (2) possible lds/sts instructions. A specific family member will have only one lds/sts combination. The ATmega328P lds/sts instruction is illustrated here with the exception that 5 bits (not 4) encode Rr/Rd. This means all 32 registers are available to the lds/sts instruction.

in r16, PINC

out PORTD, r16

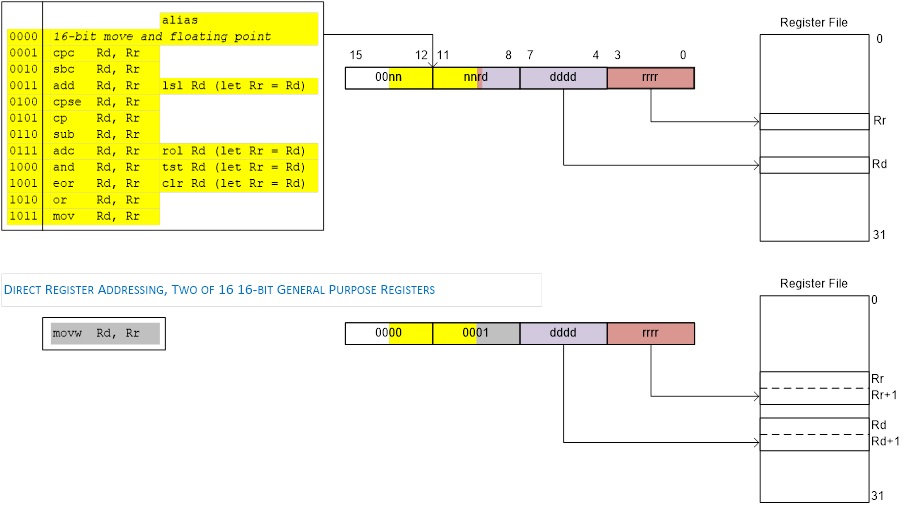

REGISTER-REGISTER INSTRUCTIONS

Data Transfer

- Register-register move byte (mov) or word (movw)

Arithmetic and Logic (ALU)

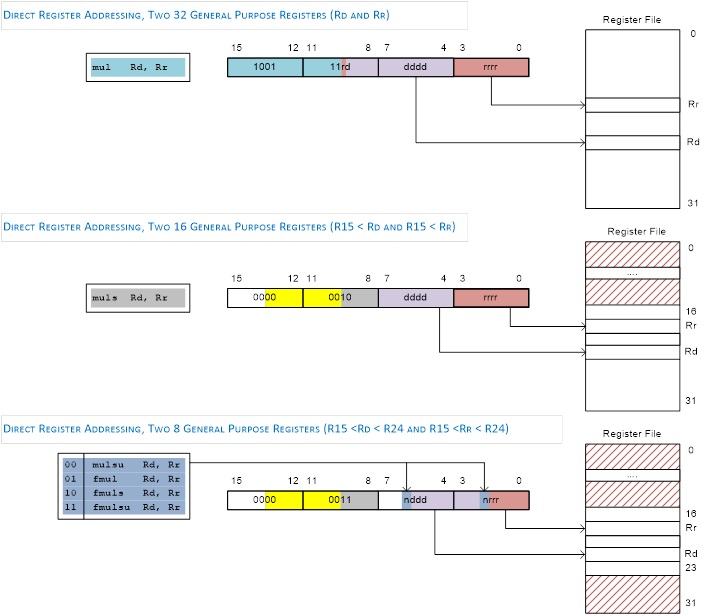

- Two’s complement negate (neg), Arithmetic add (add, adc, adiw), subtract (sub, subi, sbc, sbci), and multiply (mul, muls, mulsu, fmul, fmuls, fmulsu)

- Logical not (com), and (and, andi, cbr, tst), or (or, ori, sbr), exclusive or (eor)

- Clear (clr), set (ser), increment (inc), decrement (dec)

Bit and Bit-Test

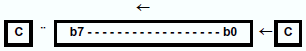

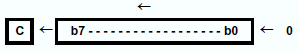

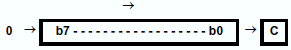

- Register logical shift left (lsl) or right (lsr); arithmetic shift right (asr); and rotate left or right (rol, ror)

- Register swap nibble (swap)

- Register bit load (bld) or store (bst) from/to T flag in the Status Register SREG

- I/O Register Clear (cbi) or set (sbi) a bit

- Clear (clFlag) or set (seFlag) a Flag bit in the Status Register SREG by name (I, T, H, S, V, N, Z, C) or bit (bclr, bset).

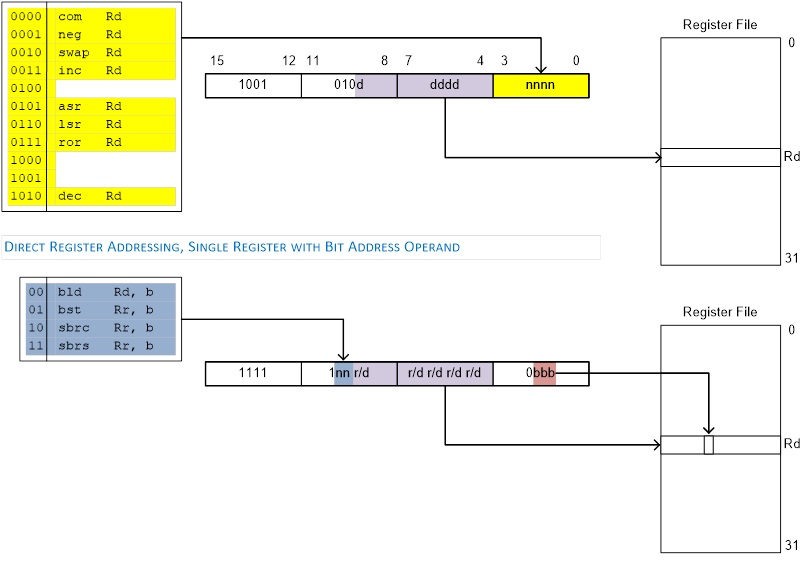

REGISTER DIRECT

In the following figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits. To generalize, the abstract terms RAMEND and FLASHEND have been used to represent the highest location in data and program space.

com r16

add r16, r17

LOAD-STORE PROGRAM EXAMPLE

Write an Assembly program to add two 8-bit numbers.

C = A + B

lds r16, A ; 1. Load variables

lds r17, B

add r16, r17 ; 2. Do something

sts C, r16 ; 3. Store answer

- Identify the operation, source operand, destination operand in the first Data Transfer instruction.

- Identify the source/destination operand in the Arithmetic and Logic (ALU) instruction.

- What addressing mode is used by the source operand, in the first instruction?

- Show contents of Flash Program Memory (mnemonics)

- Show contents of SRAM Data Memory, assuming variables are stored in sequential memory locations starting at address 010016.

- Modify the program to leave register r16 unchanged by making a copy (use r15).

SPECIAL TOPIC – HARVARD VERSUS PRINCETON ARCHITECTURE

Princeton or Von Neumann Memory Model

Program and data share the same memory space. Processors used in all personal computers, like the Pentium, implement a von Neumann architecture.

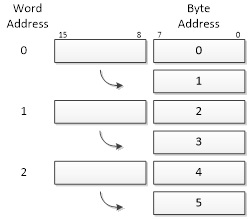

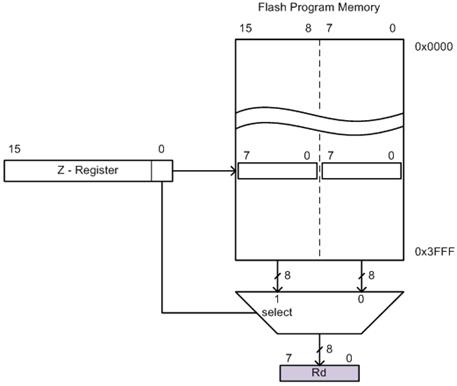

Harvard Memory Model

Program and data memory are separated. The AVR processors among others including the Intel 8051 use this memory model. One advantage of the Harvard architecture for microcontrollers is that program memory can be wider than data memory. This allows the processor to implement more instructions while still working with 8-bit data. For the AVR processor program memory is 16-bits wide while data memory is only 8-bits.

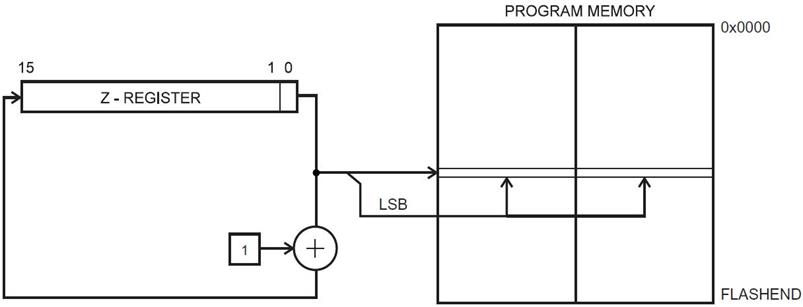

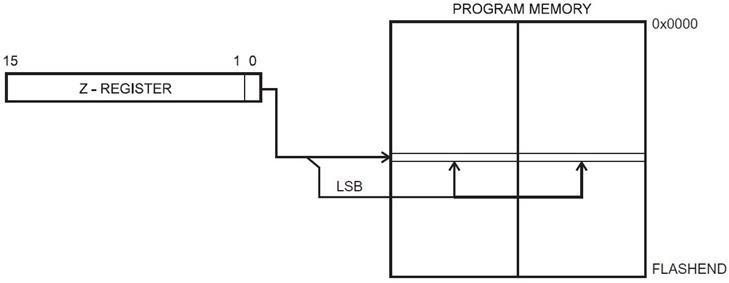

You may have already noticed that when you single step your program in the simulator of AVR Studio it is incremented by 1 each time an instruction is executed. No surprise there right? Wrong. The program memory of the AVR processor can also be accessed at the byte level. In most cases this apparent paradox is transparent to the operation of your program with one important exception. When you want to access data stored in program memory, you will be working with byte addresses not words (16-bits). The assembler is not smart enough to know the difference and so when you ask for an address in program memory it returns its word address. To convert this word address into a byte address you need to multiply it by 2. Problematically we do this by using the shift left syntax of C++ to explicitly tell the assembler to multiply the word address by 2. Remember, when you shift left one place you are effectively multiplying by 2.

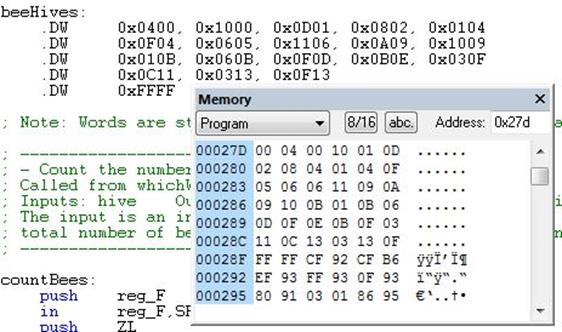

With this in mind, we would interpret the following AVR instruction as telling the AVR assembler to convert the word address of label beehives in program memory to a byte address and then to take the low order of the resulting value and put into the source operand of the instruction.

ldi ZL,low(beeHives<<1) // load word address of beeHives look-up

APPENDIX A – ATMEGA328P INSTRUCTION SET

Introduction to AVR Assembly Language Programming II: ALU and SREG

READING

The AVR Microcontroller and Embedded Systems using Assembly and C

by Muhammad Ali Mazidi, Sarmad Naimi, and Sepehr Naimi

Sections: 2.4, 5.1, 5.2, 6.5

COMPLEMENTARY READING

The following source(s) cover the same material as Chapter 2 of your textbook.

They are provided to you in case you want a different viewpoint.

ATMEL document doc8161 “8-bit AVR Microcontroller with 4/8/16/32K Bytes In-System Programmable Flash” Section 6.3.1: SREG – AVR Status Register

Table of Contents

INSTRUCTION SET ARCHITECTURE (REVIEW)

ALU – TWO OPERAND INSTRUCTIONS

- All math (+,-,×,÷) and logic (and, or, xor) instructions work with the Register File (register to register).

- Most math and logic instructions have two operands Rd, Rr with register Rd initially containing one of the values to be operated on and ultimately the result of the operation. The initial contents of Rd are therefore destroyed by this operation.

add Rd, Rr ; Rd = Rd + Rr, You may use any register (R0 – R31).

- Some math and logic operations replace the source register Rr with a constant K. Typically denoted by an “i” postfix.

subi Rd, K ; Rd = Rd – K, You may only registers (R16 – R31).

add, adc, adiw Adds two registers and the contents of the C Flag (adc only) and places the result in the destination register Rd.

sub, sbc, subi, sbci, sbiw Subtracts the source register Rs or constant K from the source/destination register Rr and subtracts with the C Flag (sbc and sbci only) and places the result in the source/destination register Rd. Think of the C Flag as the Borrow bit within this context.

mul, muls, mulsu, fmul, fmuls, fmulsu The multiplicand Rd and the multiplier Rr are two registers containing binary or fractional ( f-prefix) encoded numbers. Both numbers may be unsigned (mul, fmul), or signed (muls, fmuls). Finally, the multiplicand Rd may be signed with the multiplier Rr unsigned (mulsu, fmulsu). The 16-bit unsigned product is placed in R1 (high byte) and R0 (low byte).

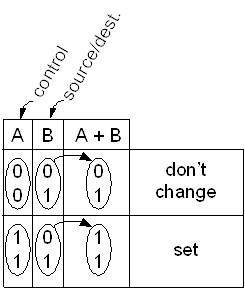

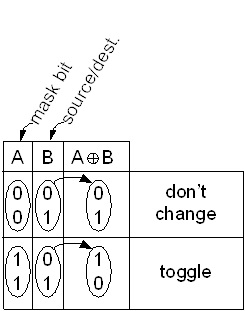

and, andi, or, ori, eor Performs the logical AND, OR, and XOR operations between the contents of register Rd and register Rr or constant K.

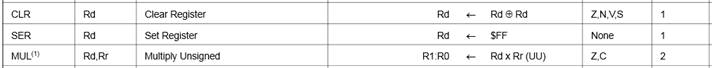

ALU – SINGLE OPERAND INSTRUCTIONS

- All single operand math and logic instructions only need a single register and usually the mnemonic alone is enough to tell you what it does.

| Mnemonic | Operation | Description |

| com | One’s complement | |

| neg | Two’s complement | |

| inc | Increment | |

| dec | Decrement | |

| clr | Clear | |

| ser | Set Register, Limited to r16-r31 | |

| tst | Test for Zero or Minus |

ALU PROGRAM EXAMPLE

Write an Assembly program to implement the polynomial expression

B = A2 + A + 41

.INCLUDE

.DSEG

A: .BYTE 1 // 8 bit input

B: .BYTE 2 // 16 bit output

.CSEG

; load

lds r16, A ; r16 with the value of A

clr r17 ; r17 with 0

ldi r18, 41 ; r18 with 41

; do something

mul r16, r16 ; r1:r0 = A^2

add r0, r16

adc r1, r17 ; r1:r0 = A^2 + A

add r0, r18

adc r1, r17 ; r1:r0 = A^2 + A + 41

; store

sts B, r0 ; answer byte ordering

sts B+1, r1 ; is little endian

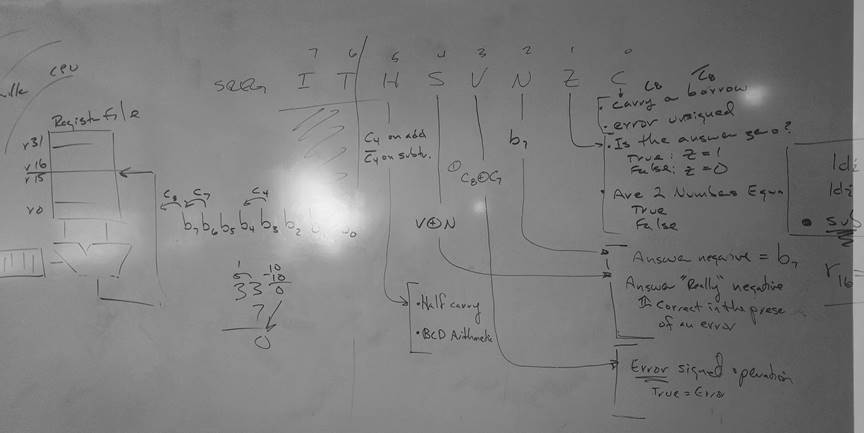

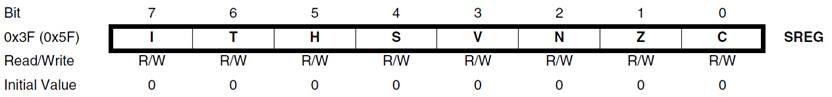

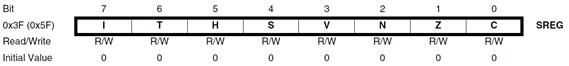

SREG – AVR STATUS REGISTER

SREG – AVR Status Register

Non ALU

- Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the reti instruction. The I-bit can also be set and cleared by the application with the sei and cli instructions. - Bit 6 – T: Bit Copy Storage

The Bit Copy instructions bld (Bit LoaD) and bst (Bit STore) use the T-bit as source or destination. A bit from a register can be copied into T (Rb -> T) by the bst instruction, and a bit in T can be copied into a bit in a register (T -> Rb) by the bld instruction.

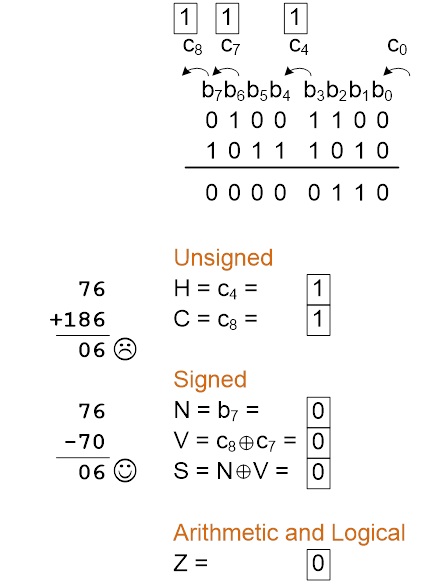

ALU

Signed two’s complement arithmetic

- Bit 4 – S: Sign Bit, S = N ⊕ V

Bit set if answer is negative with no errors or if both numbers were negative and error occurred, zero otherwise. - Bit 3 – V: Two’s Complement Overflow Flag

Bit set if error occurred as the result of an arithmetic operation, zero otherwise. - Bit 2 – N: Negative Flag

Bit set if result is negative, zero otherwise.

Unsigned arithmetic

- Bit 5 – H: Half Carry Flag

Carry from least significant nibble to most significant nibble. Half Carry is useful in BCD arithmetic. - Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic operation. Bit set if error occurred as the result of an unsigned arithmetic operation, zero otherwise.

Arithmetic and Logical

- Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation.

THE SREG OVERFLOW BIT

- The overflow bit indicates if there was an error caused by the addition or two n-bit 2’s complement numbers, where the n-1 “sign bit” is 1 if the number is negative and 0 if the number is positive. In other words, the sum is outside the range 2n 1 to 2n 1 1.

- Another way to recognize an error in addition is to observe that if you add two numbers of the same sign (positive + positive = negative or negative + negative = positive) then an error has occurred.

- An overflow condition can never result from the addition of two n-bit numbers of opposite sign (positive _ negative or negative + positive).

- Here are examples of all four cases for two 8 bit signed numbers.

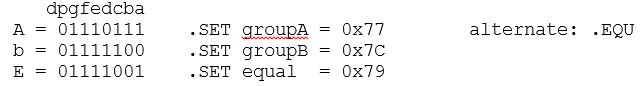

Case A B C D 0b6b5b4b3b2b1b0 0b6b5b4b3b2b1b0 1b6b5b4b3b2b1b0 1b6b5b4b3b2b1b0 0b6b5b4b3b2b1b0 1b6b5b4b3b2b1b0 0b6b5b4b3b2b1b0 1b6b5b4b3b2b1b0

The variable “bn” simply indicates some binary value and may be 1 or 0. The index of the carry bit (Cn) is equal to the carry into bit bn. For example, the carry into b0 is C0 and the carry out of an 8-bit register b7 is C8.

- Looking first at Case A, a carry cannot be generated out of the sign bit (Cn+1=0); therefore, if a carry enters the sign bit (Cn=1), the sum will be negative and the answer is wrong.

- For Case B and Case C no error can occur. Observe that in both case B and C because the numbers are contained in an n-bit (n = 8) register, we know they are in the range -2n-1 to 2n-1-1 (-128 to 127 for our two 8-bit numbers). Because one number is positive and the other negative, we further know, the answer must be correct.

- For Case D, a carry will always be generated out of the sign bit Cn+1=1 (ex. C8 = 1) with the sign bit itself set to 0; therefore, if a carry does not enter the sign bit Cn=0 (C7=1) the sum will be positive and the answer will be wrong.

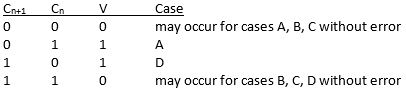

- Here is what we have discovered translated into a truth-table.

- Solving for the overflow bit (V) we have,

COMPUTING ALU STATUS REGISTER BITS – ADDITION –

COMPUTING ALU STATUS REGISTER BITS – SUBTRACTION –

- For subtract instructions (sub, subi, sbc, sbci, sbiw), including compare instructions (cp, cpc, cpi, cpse), the carry bit is equal to

and

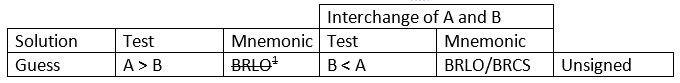

- Assume the subtract instruction sub r16, r17 has just been run by the ATmega328P microcontroller. Complete the table provided. The “difference” column should reflect the contents of register r16 after the subtraction operation (leave the answer in 2’s complement form) and not the actual difference (i.e., if done using your calculator).

Signed Unsigned r16 r17 difference relationship relationship H S V N Z C 3B 3B 00 + = + = 0 0 0 0 1 0 3B 15 26 + > + > 0 0 0 0 0 0 15 3B F9 F6 F6 F9 15 F6 F6 15 68 A5 A5 68 - Use AVR Studio simulation software to check your answers.

Introduction to AVR Assembly Language Programming II: Branching

READING

The AVR Microcontroller and Embedded Systems using Assembly and C

by Muhammad Ali Mazidi, Sarmad Naimi, and Sepehr Naimi

Sections: 3.1

ADDITIONAL READING

Introduction to AVR assembler programming for beginners, controlling sequential execution of the program http://www.avr-asm-tutorial.net/avr_en/beginner/JUMP.html

Table of Contents

INSTRUCTION SET ARCHITECTURE (REVIEW)

The Instruction Set Architecture (ISA) of a microprocessor includes all the registers that are accessible to the programmer. In other words, registers that can be modified by the instruction set of the processor. With respect to the AVR CPU illustrated here , these ISA registers include the 32 x 8-bit general purpose resisters, status resister (SREG), the stack pointer (SP), and the program counter (PC).

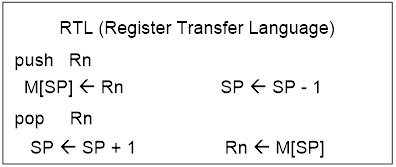

Data Transfer instructions are used to load and store data to the General Purpose Registers, also known as the Register File. Exceptions are the push and pop instructions which modify the Stack Pointer. By definition these instructions do not modify the status register (SREG).

Arithmetic and Logic Instructions plus Bit and Bit-Test Instructions use the ALU to operate on the data contained in the general purpose registers. Flags contained in the status register (SREG) provide important information concerning the results of these operations. For example, if you are adding two signed numbers together, you will want to know if the answer is correct. The state of the overflow flag (OV) bit within SREG gives you the answer to this question (1 = error, 0 no error).

Control Transfer Instructions allow you to change the contents of the PC either conditionally or unconditionally. Continuing our example if an error results from adding two signed numbers together we may want to conditionally (OV = 1) branch to an error handling routine. As the AVR processor fetches and executes instructions it automatically increments the program counter (PC) so it always points at the next instruction to be executed.

INSTRUCTION SET (REVIEW)

The Instruction Set of our AVR processor can be functionally divided (or classified) into the following parts:

- Data Transfer Instructions

- Arithmetic and Logic Instructions

- Bit and Bit-Test Instructions

- Control Transfer (Branch) Instructions

- MCU Control Instructions

JUMP INSTRUCTIONS

- There are two basic types of control transfer instructions – Unconditional and Conditional.

- From a programmer’s perspective an unconditional or jump instruction, jumps to the label specified. For example, jmp loop will unconditionally jump to the label loop in your program.

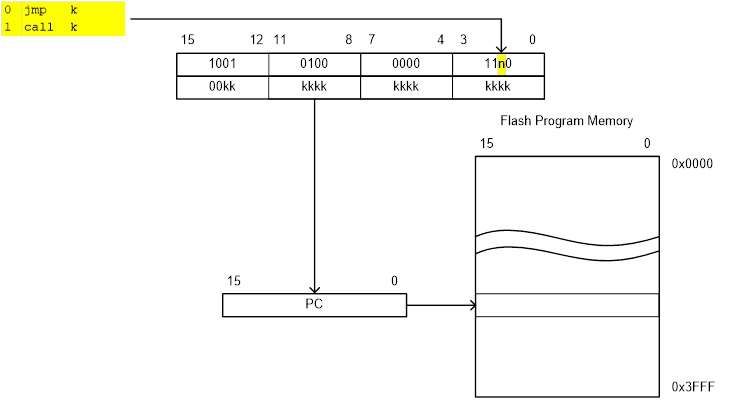

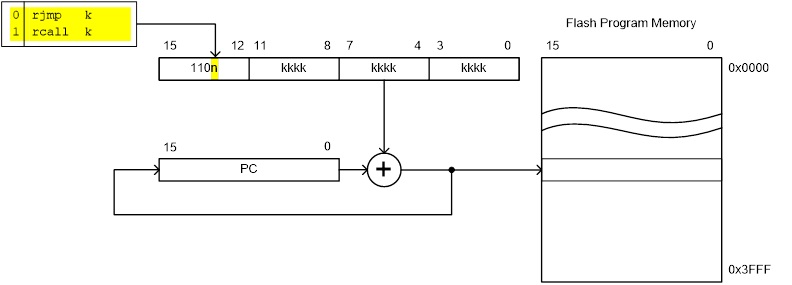

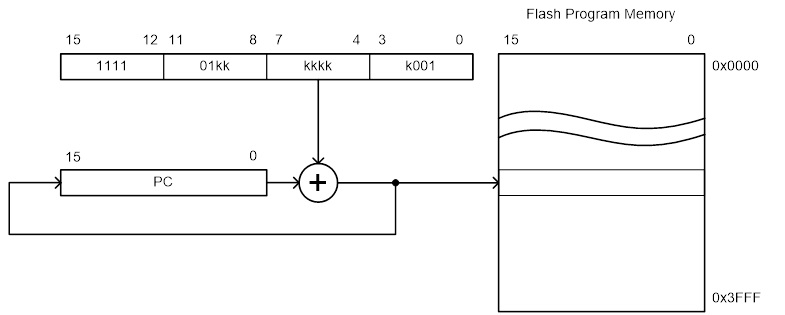

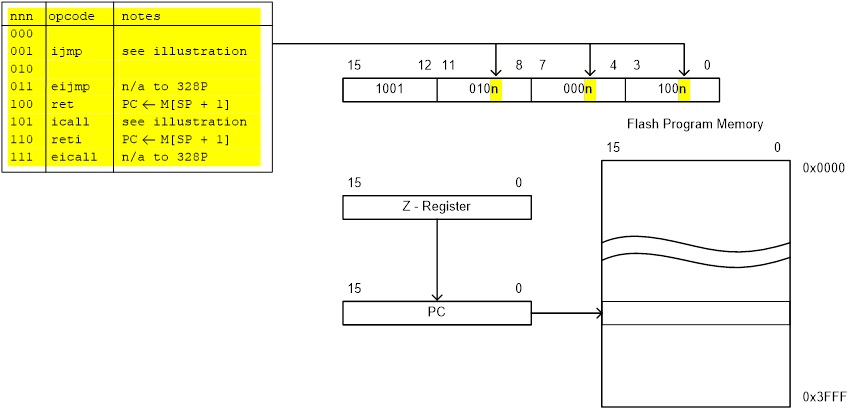

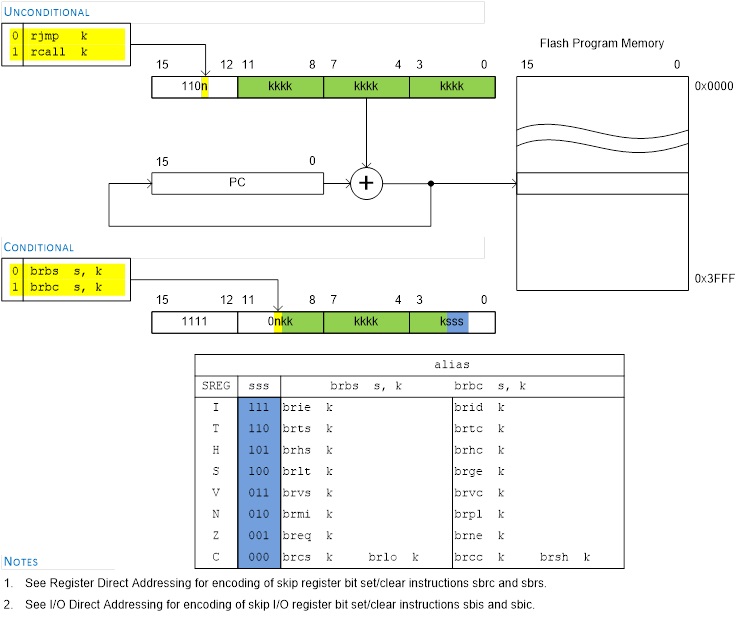

- Here are the unconditional control transfer “Jump” instructions of the AVR processor

Direct jmp, call Relative (1) rjmp, rcall Indirect ijmp, icall Subroutine & Interrupt Return ret, reti

Note:

- Jump relative to PC + (

, where k = 12)

PC-2048 to PC+2047, within 16 K word address space of ATmega328P

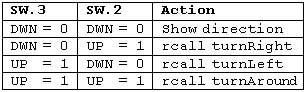

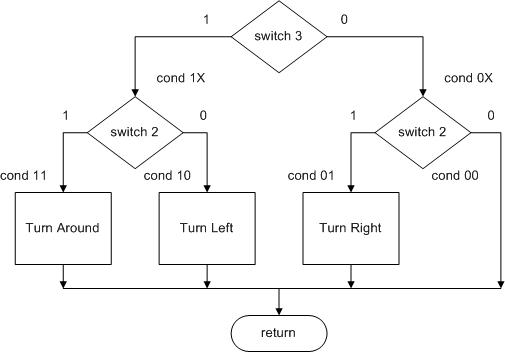

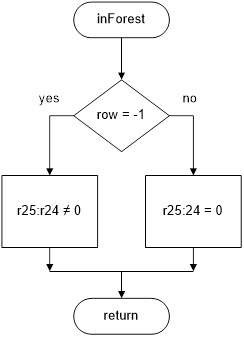

HOW THE DIRECT UNCONDITIONAL CONTROL TRANSFER INSTRUCTIONS JMP AND CALL WORK